PCIe – LTSSM Detect

1. Detect 状态

- 目的 :

- 检查对端是否存在

- 存在的子状态 :

Detect.QuietDetect.Active

- 状态跳转图片和文字如有冲突,以图片为准,图片更新更加频繁

2. Detect.Quiet

该子状态是任何复位(功能级别复位除外)或上电事件后的初始状态,必须在复位后 20 毫秒内进入。

2.1 Detect.Quiet时行为

- 让发射机电压处于 EI (Electrical Idle) 状态

- 链路速度切换为2.5GT/s

- 如果从其它状态跳到该状态时(如从 Recovery 跳转到 Detect),速度不是 2.5 GT/s,则必须等待 1ms,在此期间,速度要切回到 2.5 GT/s

- TS1/2 中建议的速度不会改变,即下一次TS交互时建议的速度还是上次训练所支持的速度

- 物理层状态位 (LinkUp = 0,内部的状态位) 会通知数据链路层,链接不可用。当 Link Training 完成时,LinkUp = 1,从而通知数据链路层和流控制初始化开始其链路初始化部分。

- 初始化寄存器和变量

2.1.1 初始化寄存器和变量

- 以下寄存器清0

- Link Status 2 寄存器中的下列 field 清 0

- bit[1] : Equalization 8.0 GT/s Complete

- bit[2] : Equalization 8.0 GT/s Phase 1 Successful

- bit[3] : Equalization 8.0 GT/s Phase 2 Successful

- bit[4] : Equalization 8.0 GT/s Phase 3 Successful

- 16.0 GT/s Status 寄存器中的下列 field 清 0

- bit[0] : Equalization 16.0 GT/s Complete

- bit[1] : Equalization 16.0 GT/s Phase1 Successful

- bit[2] : Equalization 16.0 GT/s Phase2 Successful

- bit[3] : Equalization 16.0 GT/s Phase3 Successful

- 32.0 GT/s Status 寄存器中的下列 field 清 0

- bit[0] : Equalization 32.0 GT/s Complete

- bit[1] : Equalization 32.0 GT/s Phase1 Successful

- bit[2] : Equalization 32.0 GT/s Phase2 Successful

- bit[3] : Equalization 32.0 GT/s Phase3 Successful

- 64.0 GT/s Status寄存器的下俩 field 清0 (gen6新增)

- bit[0] : Equalization 64.0 GT/s Complete

- bit[1] : Equalization 64.0 GT/s Phase1 Successful

- bit[2] : Equalization 64.0 GT/s Phase2 Successful

- bit[3] : Equalization 64.0 GT/s Phase3 Successful

- Device Status3寄存器的下列 field

- Remote L0p Supported -> 对方是否支持 L0p 特性

- 以下变量清零

- LinkUp (物理层链路是否已经就绪)

- use_modified_TS1_TS2_Ordered_Set

- 下列变量在 PCIe 2.0以下不会存在

- directed_speed_change

- 1 : 设备希望更改数据传输速度

- 0 : 设备不希望更改数据传输速度

- upconfigure_capable

- 跟 Link Upconfigure Capability 有关,当设备发送 TS2 (Symbol 4 bit[6] : Link Upconfigure Capability 为1) 且收到 8 个连续的 TS2 (Link Upconfigure Capability 为1)后,会把 upconfigure_capable 置为1

- Link Upconfigure Capability 表示当一个较宽的链路在减少链路宽度后,是否有能力重新恢复到原先较宽的链路宽度。1 为有能力,0 为无能力

- idle_to_rlock_transitioned

- idle 向 Recovery.RcvrLock 跳转了多少次

- idle 包括 Recovery.Idle 或者 Configuration.Idle

- select_deemphasis

- 对 Downstream port 来讲,由硬件决定

- 对 Upstream port 来讲,变量使用 Link Control 2 寄存器中保存的 Selectable Preset/De-emphasis (bit[6])值

- equalization_done_8GT_data_rate

- equalization_done_16GT_data_rate

- equalization_done_32GT_data_rate

- perform_equalization_for_loopback

- 以下为gen6新增

- Flit_Mode_Enabled -> 是否支持Flit模式

- L0p_capable -> 是否支持L0p

- SRIS_MODE_Enable -> 使用使用SRIS

- equalization_done_64GT_data_rate -> 是否做完64.0GT/s下的eq

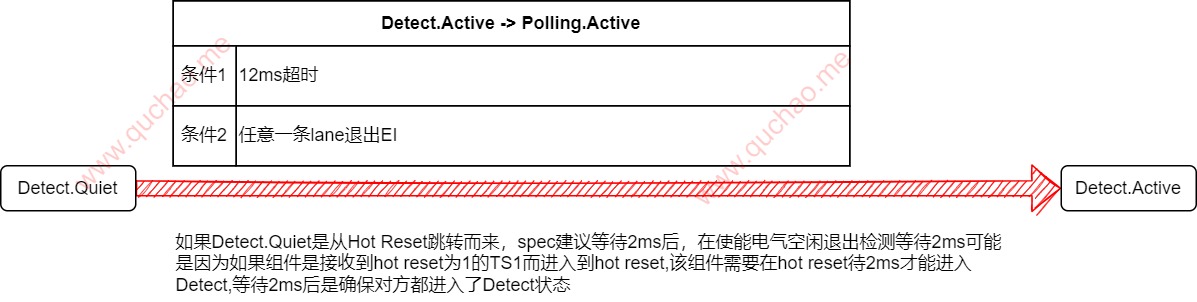

2.2 Detect.Quiet状态跳转

- Detect.Quiet可以实现的跳转

- Detect.Quiet -> Detect.Active

- Detect.Quiet -> Detect.Active

2.2.1 Detect.Quiet -> Detect.Active

| 条件 | 跳转原因 |

|---|---|

| 条件1 | 12 ms 超时 |

| 条件2 | 或者任意一条 lane 没有处于 EI 状态。 – note : 任意一条 lane 没有处于 EI 状态,可能是对端的 LTSSM 已经进入了其它状态 |

3. Detect.Active

3.1 Detect.Active时行为

- 发射机在所有未配置过 (可能就是 link,lane 这些还没有配置) 的 lane (这些 lane 必须可以形成一条或者多条) 上执行 Receiver Detection Sequence (接收机检测序列)

- 如果不是所有 lane 都检测到 Receiver, 那么会等待 12 ms 后,再次发送接收机检测序列,如果连续两次检测到的 Receiver 都一样,则会跳转到下一个状态 (除非两次检测到的 Receiver 都是0)

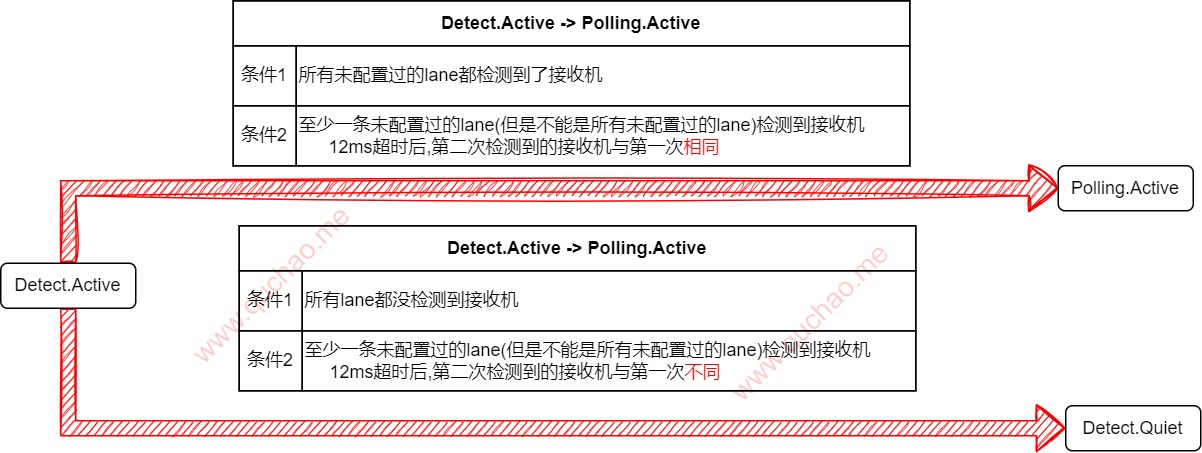

3.2 Detect.Active状态跳转

- Detect.Active可以实现的跳转

- Detect.Active -> Polling

- Detect.Active -> Detect.Quiet

3.2.1 Detect.Active -> Polling

| 条件 | 跳转原因 |

|---|---|

| 条件1 | 在所有未配置过的 lane 都检测到接收机 (Receiver) |

| 条件2 | 至少一条未配置过的lane(但是不能是所有未配置过的lane)检测到接收机,12ms超时后,第二次检测到的接收机与第一次相同 – note : 有的 lane 检测到 Receiver, 有的 lane 没有检测到 Receiver, 可能有的 lane 很快就检测到了,有的 lane 检测 Receiver 就比较慢,所以需要 12 ms 后在检测一次,确保就是这些 lane 连上了东西 (不一定是接收机,也有可能是 50 欧姆电阻等等) – 没有检测到 Receiver 的 lane 必须: + 如果可以跟新的 LTSSM 关联 (可选的特性),则要与新的 LTSSM 关键。 + 所有 lane 都不能够与新的 LTSSM 关联的话,则这些 lane 必须要处于 ei 状态 + 在 LTSSM 重新回到 Detect 状态时,这些 lane 必须从新跟 LTSSM 关联 + 在向 ei 状态转变时不需要发送 EIOS,此时就算发了对方也收不到 |

3.2.2 Detect.Active -> Detect.Quiet

| 条件 | 跳转原因 |

|---|---|

| 条件1 | 任意一条 lane 都没有检测到 Receiver note : 即所有 lane 都没有检测到 Receiver,没有检测到 Receiver, 发东西也没用,就不会往下一个状态跳转 |

| 条件2 | 12 ms后, 再次检测到 Receiver 的 lane 同上次不一样 note : 如果再次检测到的 Receiver 还是不一样,则还需要等待 12 ms后,发送接收机检测序列,确保 lane 上连了东西的都正确的找出来了 |

4. 例子

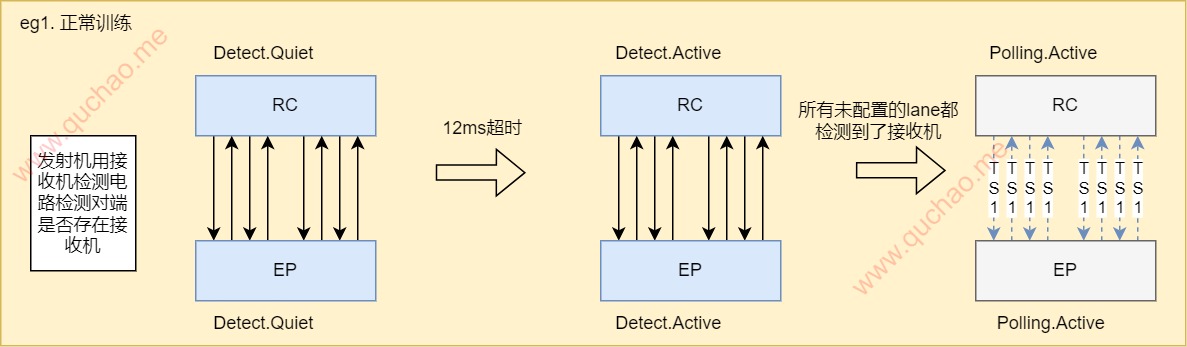

4.1 正常训练 (x4接x4)

- 刚开始RC跟EP是连接上的,通电,RC和EP的LTSSM都是处于

Detect.Quiet - 由于所有lane都是正常的,不存在哪条lane会先退出EI,所以在12ms超时后,RC和EP进入

Detect.Active,但是RC和EP谁先进入,这个不能保证,如果RC和EP的LTSSM同时开始工作,进入Detect.Active的时间点比较接近。 - 在

Detect.Active状态,执行接收机检测序列,检测对端是否等效为50欧姆负载。所有没有配置的lane都检测到了接收机,进入Polling.Active,准备发送TS1