cadence IC系列使用(4)版图

系统:redhat 6.5

cadence IC版本:IC617

库:FreePDK15

模型:PTM-MG 7nfet 7pfet

版图验证工具:calibre(mentor)

仿真工具:hspiceD(synopsys)

本网页图片较多,可能加载会比较缓慢,本教程只是介绍一下绘制版图的方法,而且不是按照平面型工艺绘制的,所以绘制版图时会比一般教程复杂一些,请不要纠结文中具体的数字,这都是我经过反复尝试弄出来的(主要是不断进行drc验证并不断修改,后期熟悉了规则文件后就会轻松很多)。

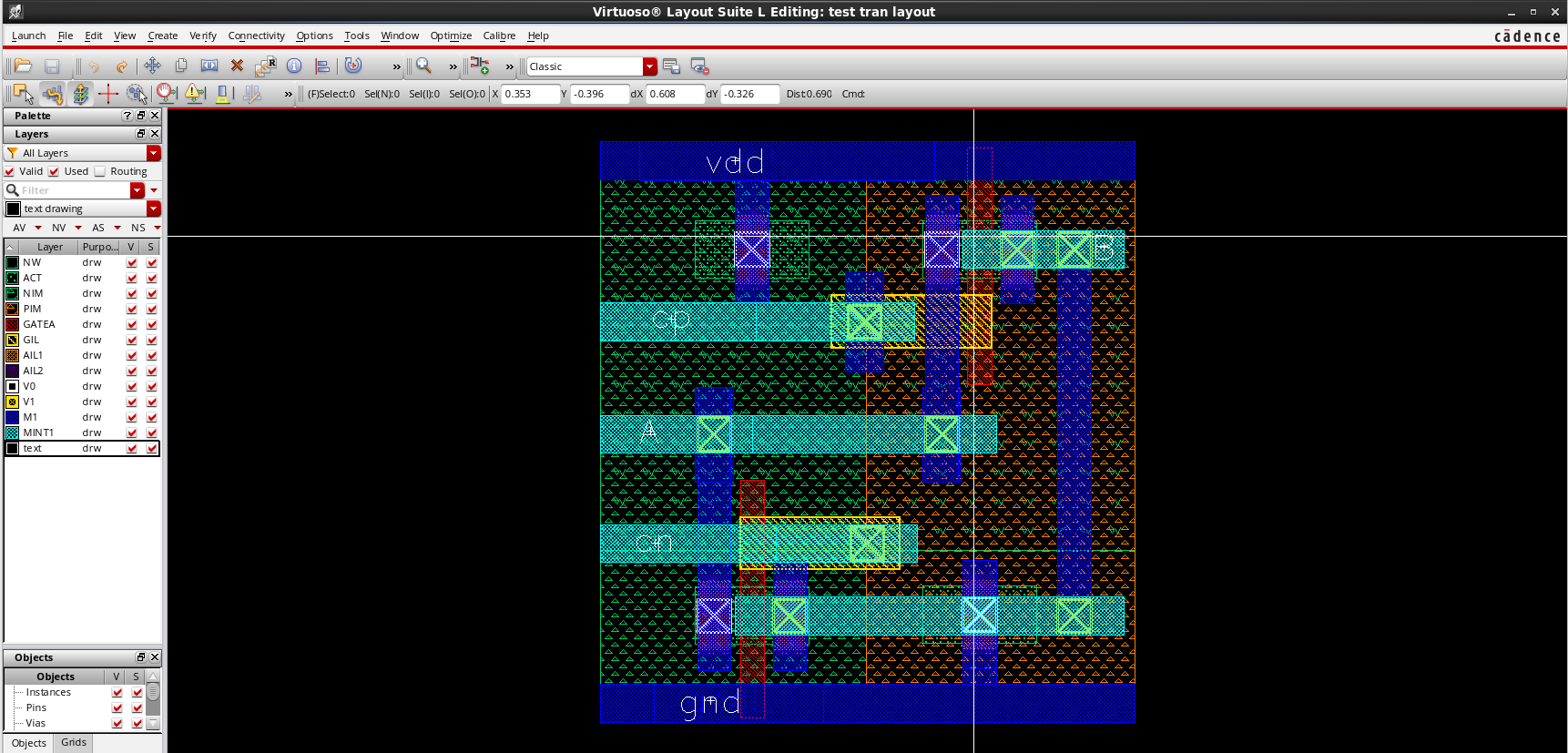

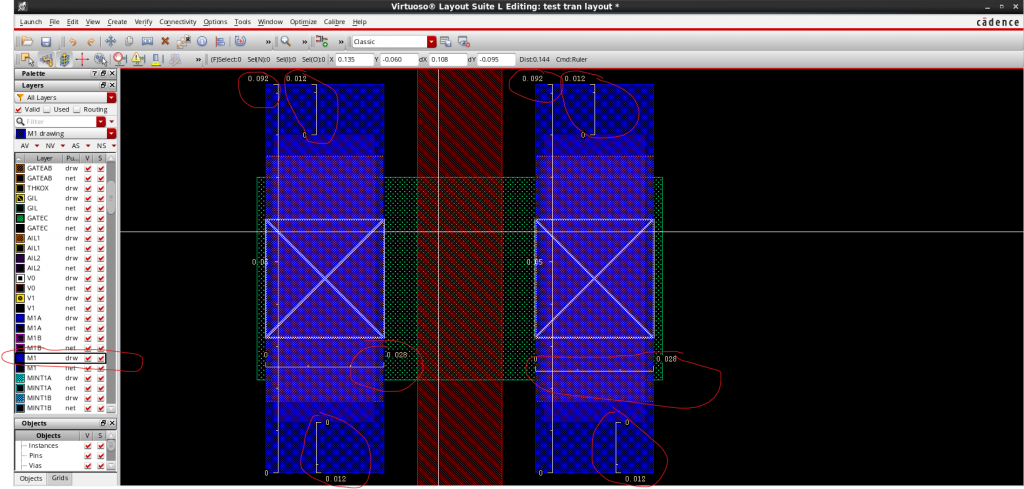

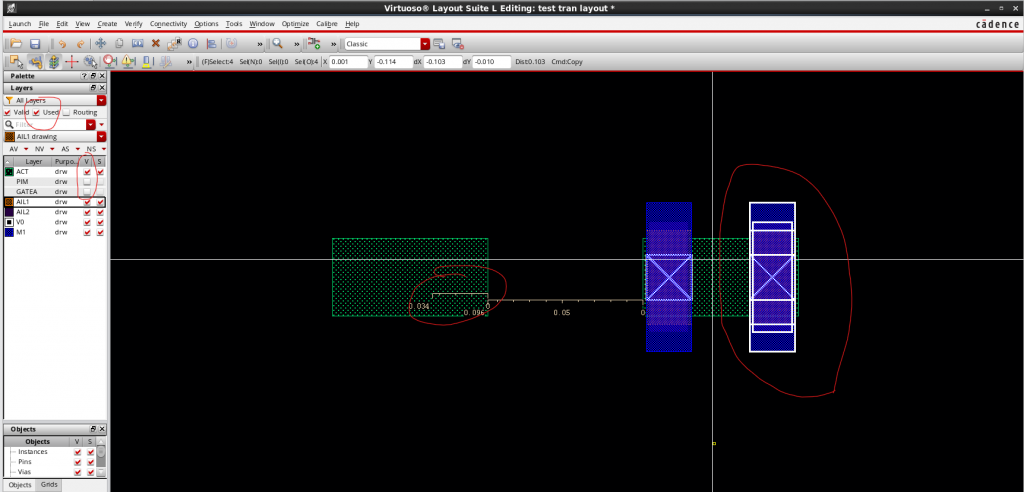

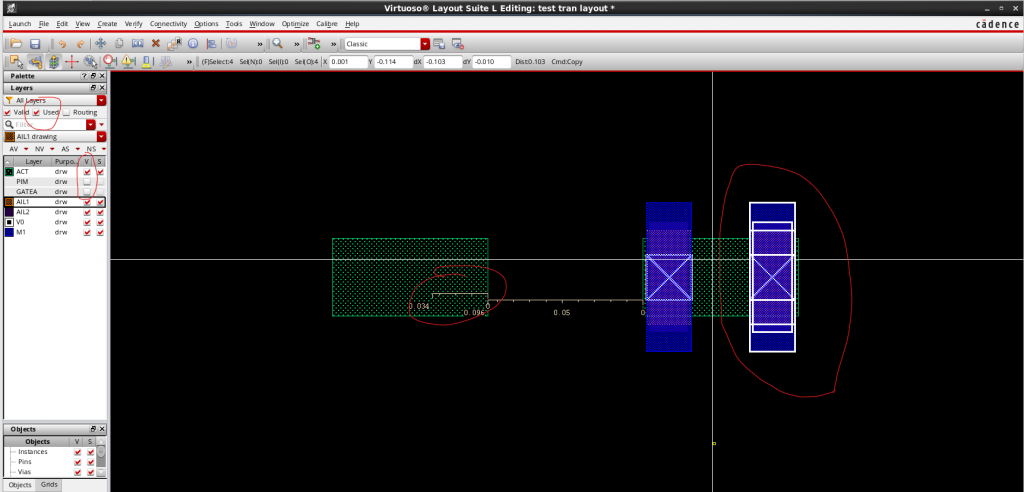

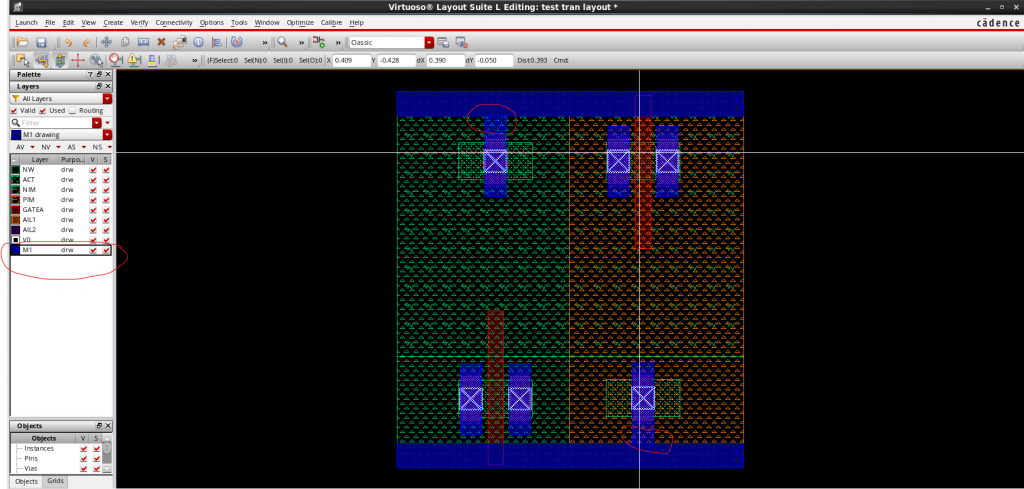

这是最终的效果图

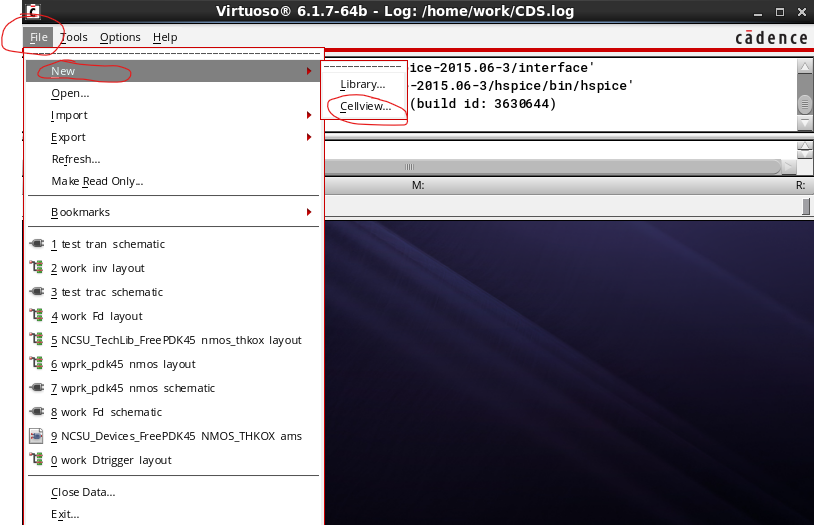

先启动 cadence ,在 Linux 终端中输入 virtuoso & ,如果是 51 版本,则使用 ifcb & 启动,这里 & 表示启动后在后台运行。 然后 选择 File — New — Cellview 。

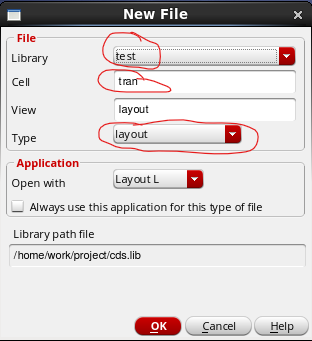

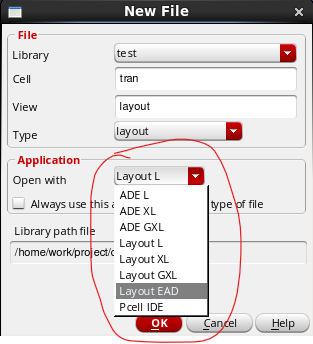

选择正确的 Library(库)、Cell (元件),Type 为 layout ,选择后会默认将 View 改为 layout。 Open with 可以选择 Layout L, Layout L 只会打开版图界面,Layout XL, Layout GXL , Layout EAD 会打开原理图和版图界面。

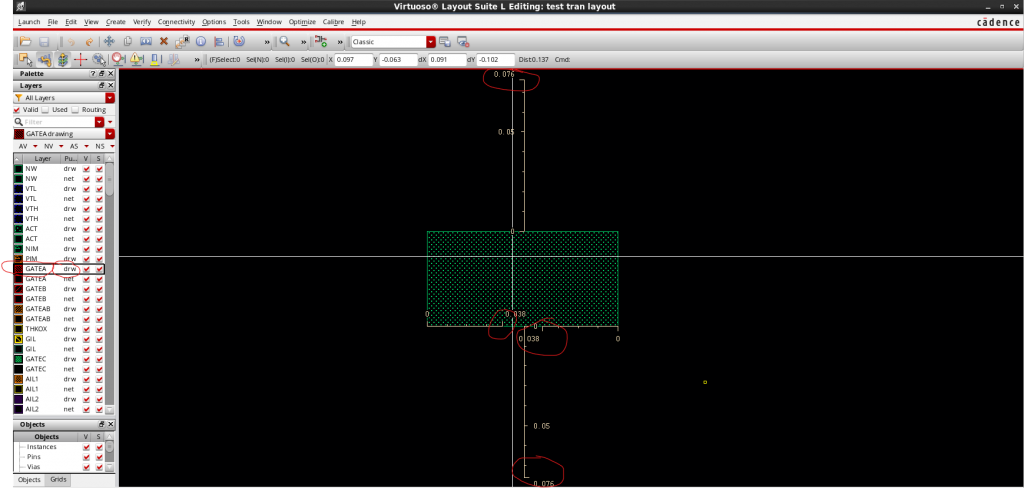

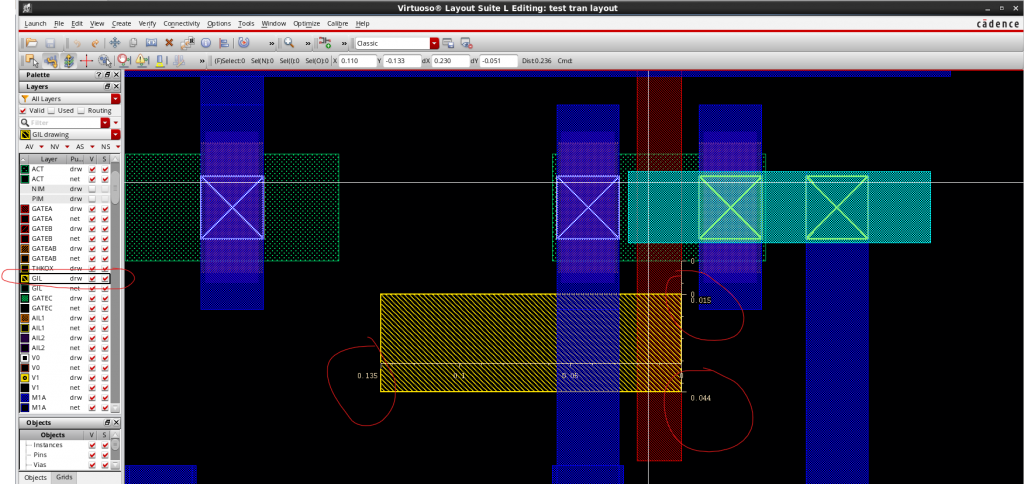

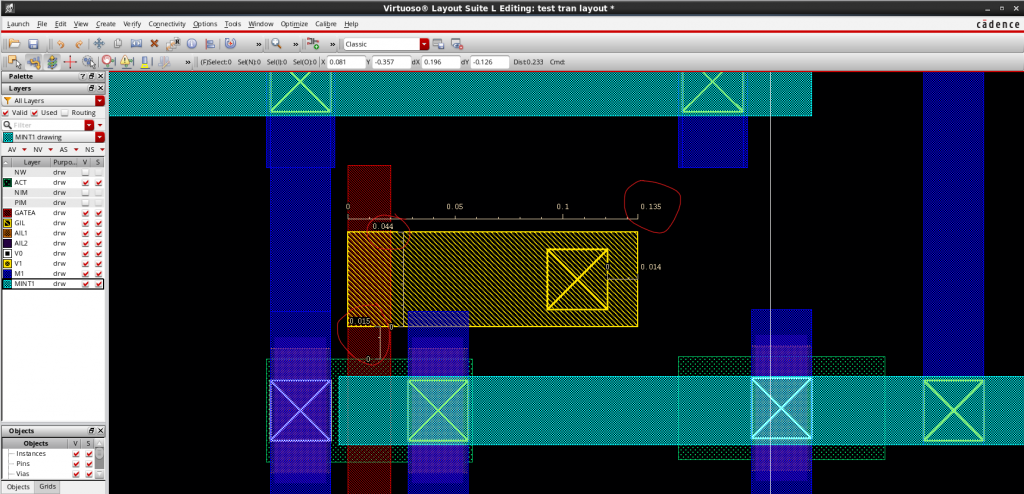

下图就是绘制版图的界面。注意,这里只是示范一下画版图的一些过程,对于版图中具体的距离可以不必在意。

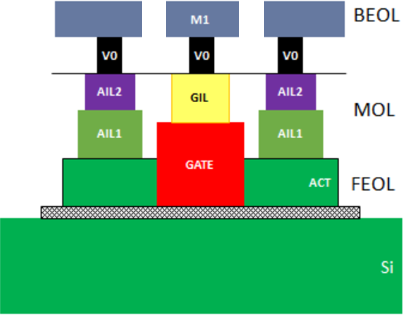

由于用的是 FreePDK 15 库,这个库不是采用平面 CMOS 工艺,这里有关于这个库的详细介绍。画版图时主要是参考下图画的,最下面绿色的硅衬底,绿色上面的灰色的是绝缘层,ACT 是有源层,AIL1 有源互联层1,ALT2 是有源互连层2,GATE 是栅极,M1 是金属层,v0 是连接AIL2和M1的通孔。

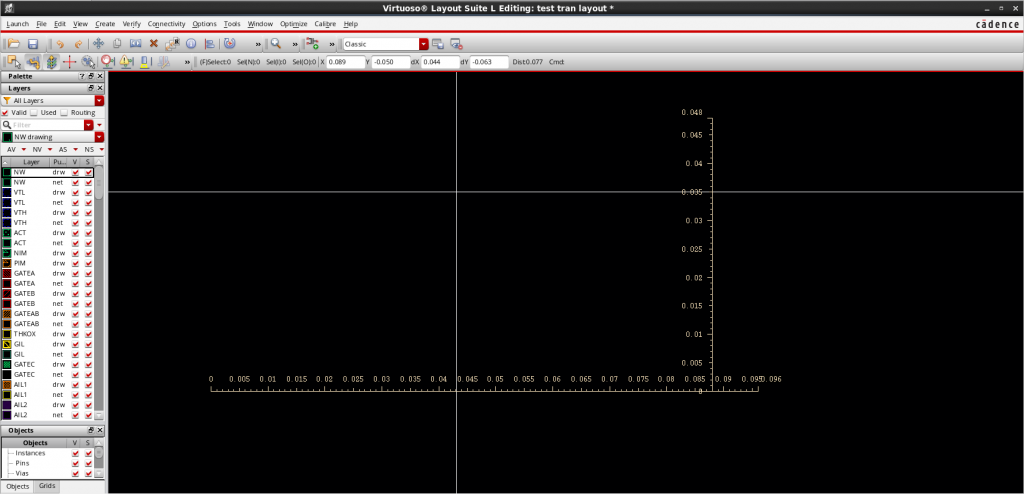

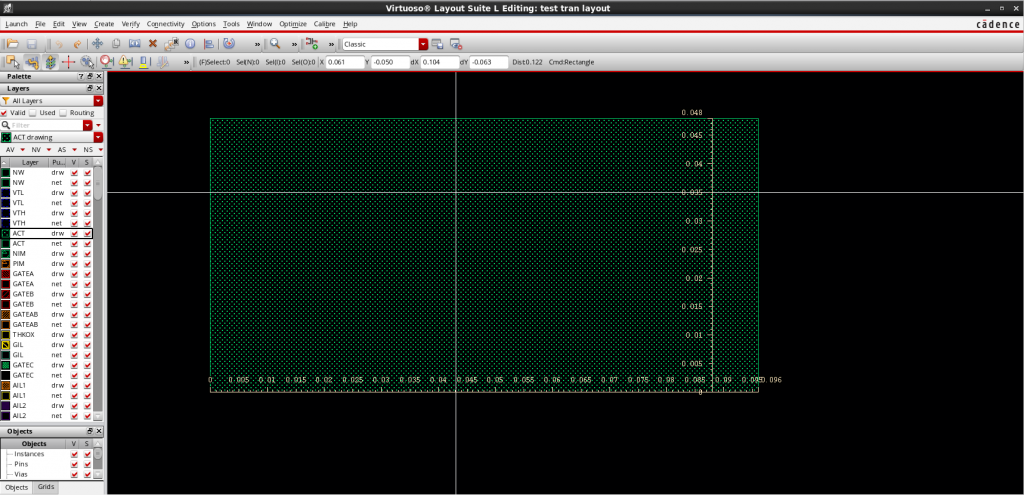

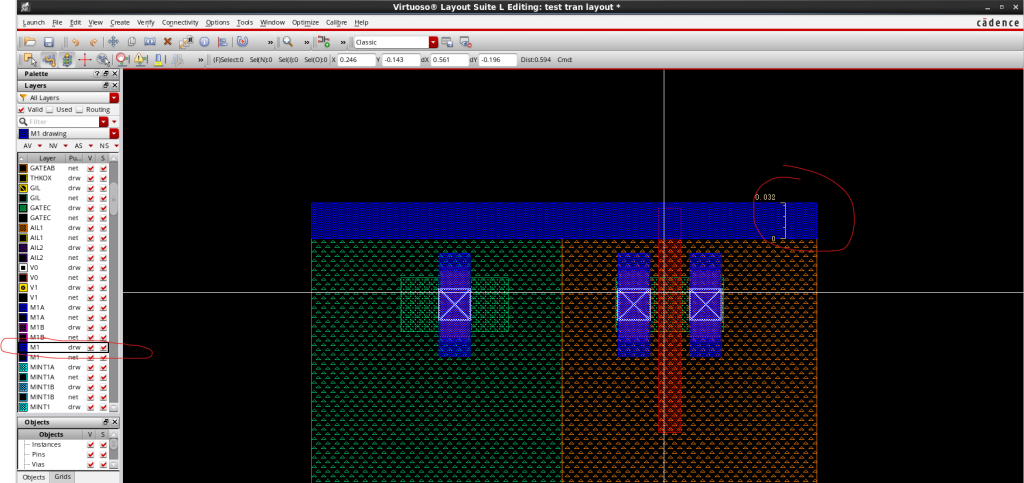

绘制版图时,图层的顺序不重要,也就是说你无论你是先画衬底还是先画有源层,都没有影响。那我们就先画有源层,有源层包括源区、漏区和沟道,在上文的原理图中,无论是 PMOS 还是 NMOS 我们设置的沟道的长都是 20 nm,宽都是 48 nm,在画版图时,就得对应,不然在后面进行 LVS(版图原理图一致性检查)会出错。在绘制版图界面,小写 k 是标尺,大写 K (shift + k)是清除标尺,首先我们按 小写 k 绘制标尺,宽为 96 nm,长为 48 nm,这里的宽是在满足规则下,能画下有源区和沟道的最小宽度,当然你也可以改为其它的,如果有错,在后面验证时在进行更改。

然后选择 ACT (有源)层,并且后面为 Drw(Drawing绘制) 的图层,后面 net 是与连线有关,pin 是与端口有关,点击 Create — shape — Rectangle,快捷键为小写 r,不是大写的 R,即可绘制有源层。

矩形起点可以选在标尺的末端,使得画出来的图形是 96 nm * 48 nm的,这里需要注意的是,尽可能将版图的中心与坐标原点相重合,这样在调用的时候就不会出现鼠标箭头跟版图离的太远的情况,在调用已经画好的版图时,鼠标箭头应该是这里的坐标原点重合的。

然后按 shift + k 清除标尺,然后像下图那样,上下用标尺标出 76 nm 的位置,有源区内部距离左右 38 nm 的位置,因为在规则文件中有明确规定栅极的长为 0.2 um,而有源区的宽(上下距离)为 48 nm ,所以需向栅极需要向两边延伸 76 nm(2*0.076+0.048 = 0.2),由于有源区下方就是沟道,而沟道的长度为 20 nm(也为栅极的宽),所以据左右 38 nm(0.038*2+0.02=0.096)。

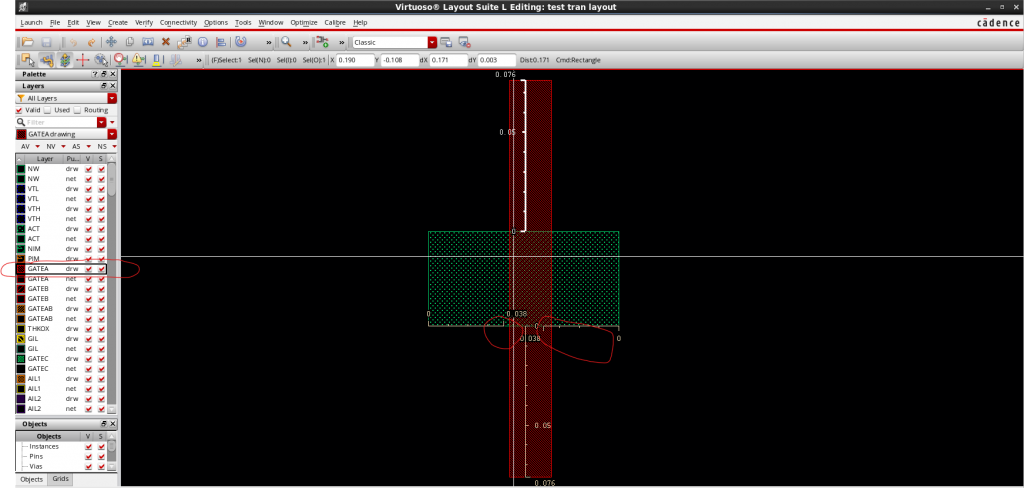

选择 GATEA Drw 图层,按小写 r ,绘制矩形,如果出现下面的情况,即画的图形偏了,或者画的太大了。

可以按小写 m (View — Move)移动图形(若大小合适),或者小写 s(View — Stretch) 的选择延伸命令。这里我选择将两条边进行延伸操作,在操作过程中,可以滑动鼠标滚轮放大缩小图形以使得刚好能对上(如果图形太小,操作时很有可能是没有完全对上的)。

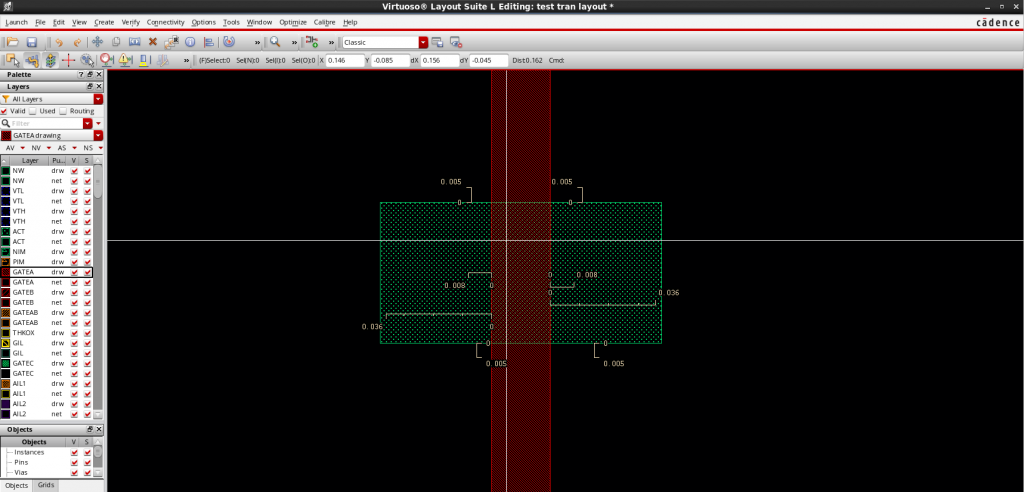

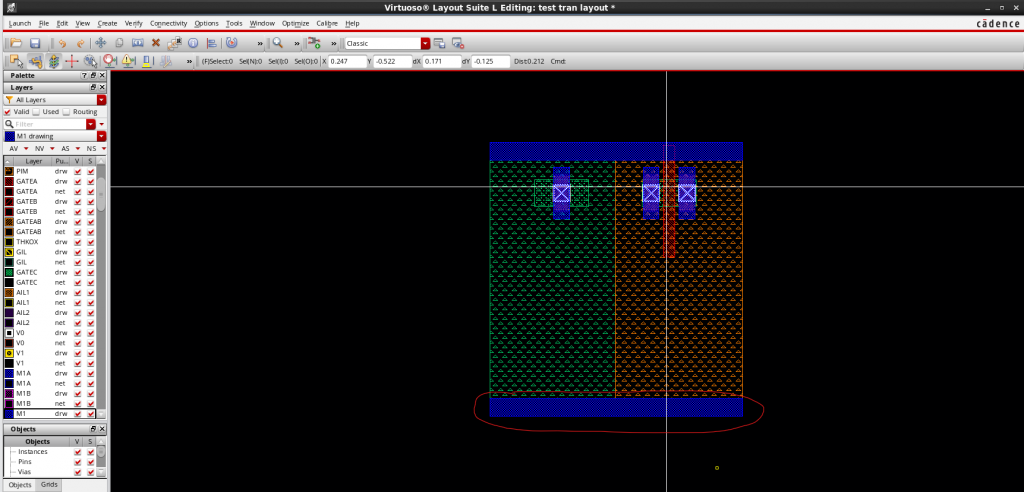

接着画源漏,按照规则(这些规则画多了就会熟悉),源漏距离沟道至少 8 nm,先清除标尺(shift + k),在标出据沟道 80 nm的地方,并且源漏的超过有源区 5 nm,在有源区上下方标出 5 nm 的位置,源漏的宽为 28 nm (左右距离) ,同样用标尺做好标记。如下图所示。

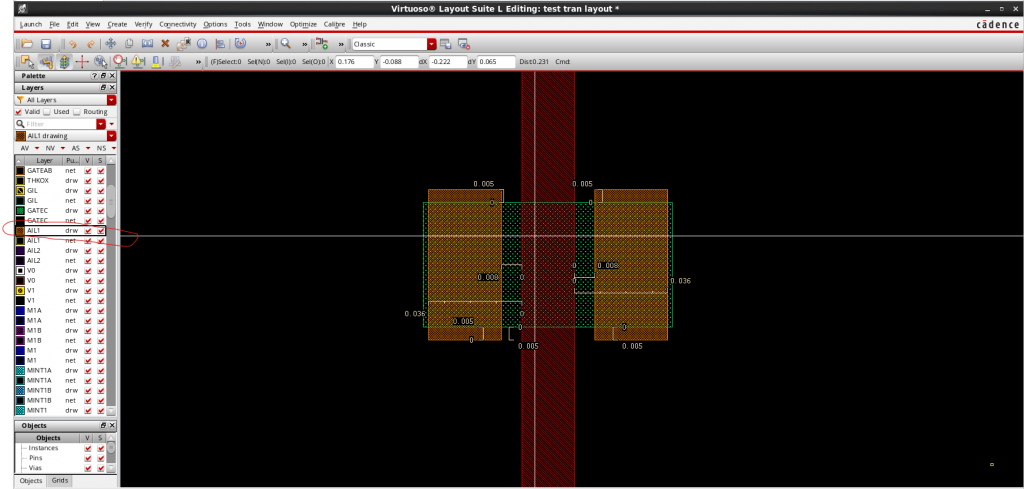

选择 AIL1 Drw 图层 ,按小写 r 绘制矩形 ,如下图所示,如果没有对上,可以使用移动或者延伸使得图形在指定位置。

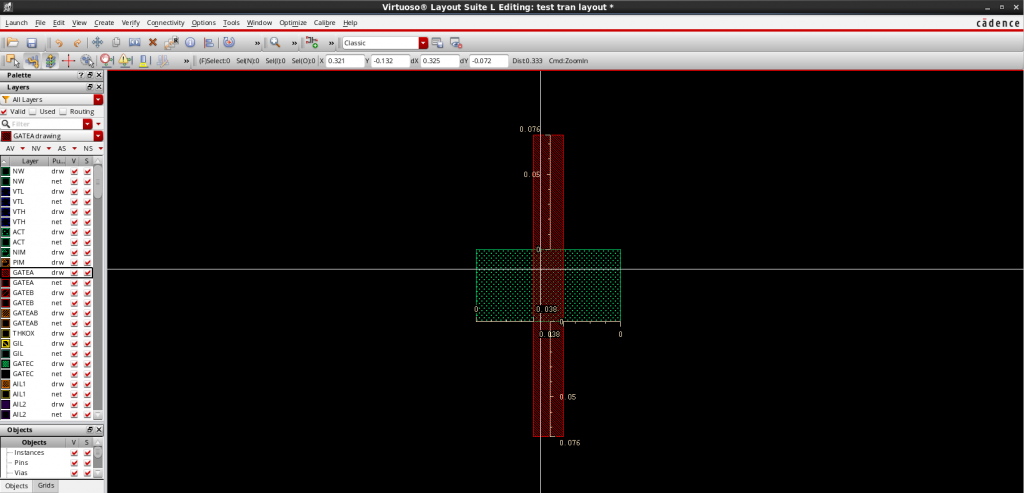

接下来画 AIL2 Drw 层 (栅极互连层 2 ),长为 68 nm ,宽为 24 nm ,各个距离如下所示。

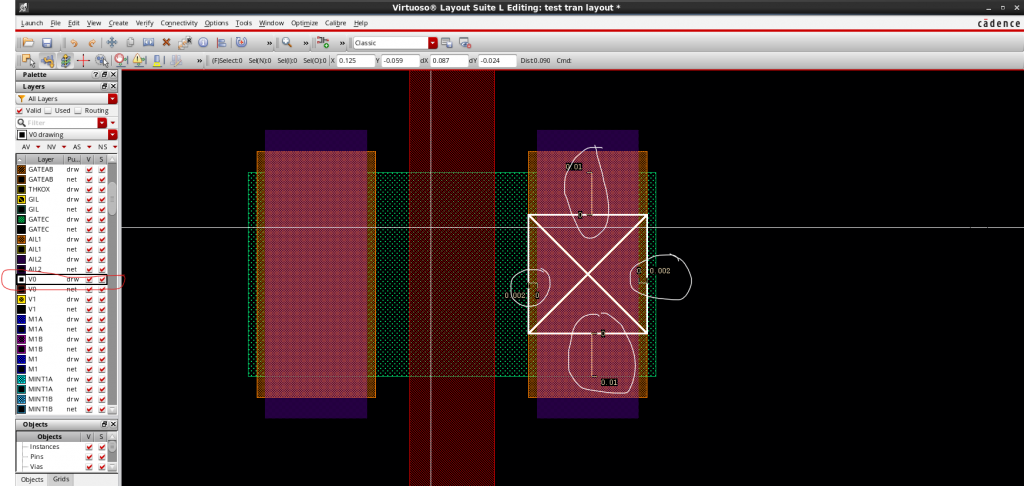

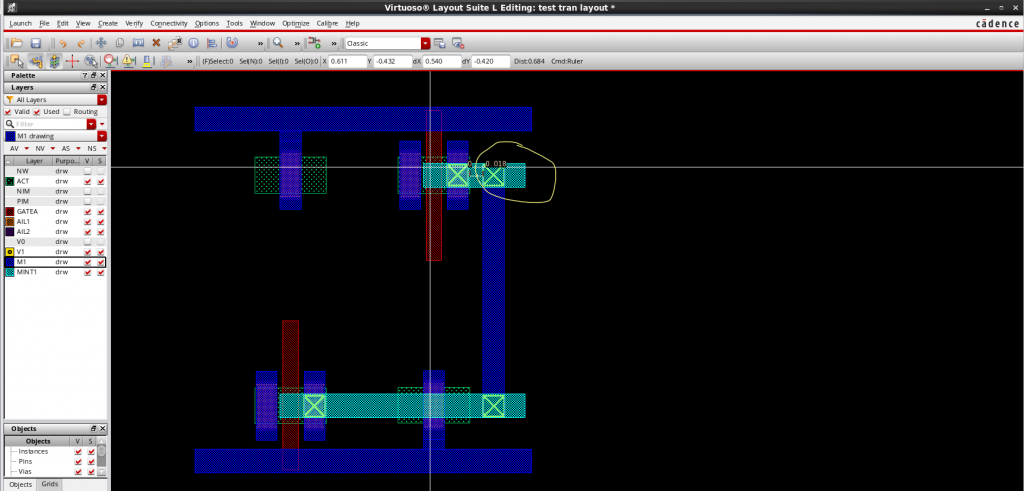

然后画过孔,按照规则,孔的长宽最小为 28 nm * 28 nm ,先用 V0 Drw 图层画一个 28 nm * 28 nm 的正方形,然后按小写的 m 移动到下面这个位置(在 AIL2 层中间,两边与 AIL1 层重合)。

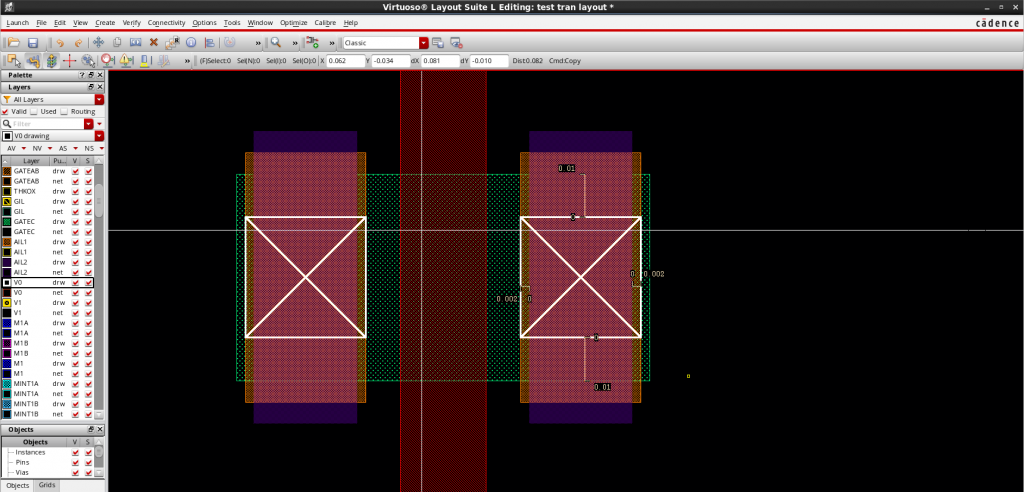

按小写的 c ,选择上面用 V0 层画的方向,然后复制到左边,如下图所示。

然后画金属层,选择 M1 Drw 层,绘制 28 nm * 92 nm 的矩形,移到下图的位置,两边与 AIL1 重合,两头超过 AIL2 12 nm ,在旁边的图层我们可以看到有 M1A Drw , M2A Drw , 它们都是金属一层,只是用了不同的颜色来表示,并且它们在后面的 drc 验证时,是不会验证的,也就是说如果M1A 和 M1B 连接在了一起,就表示它们之间短路了,如果 M1A 和 M1B 相距 1 nm ,在进行 Drc 验证时,也不会报错,但是相距 1 nm的线间距在实际中肯定是弄不出来的。

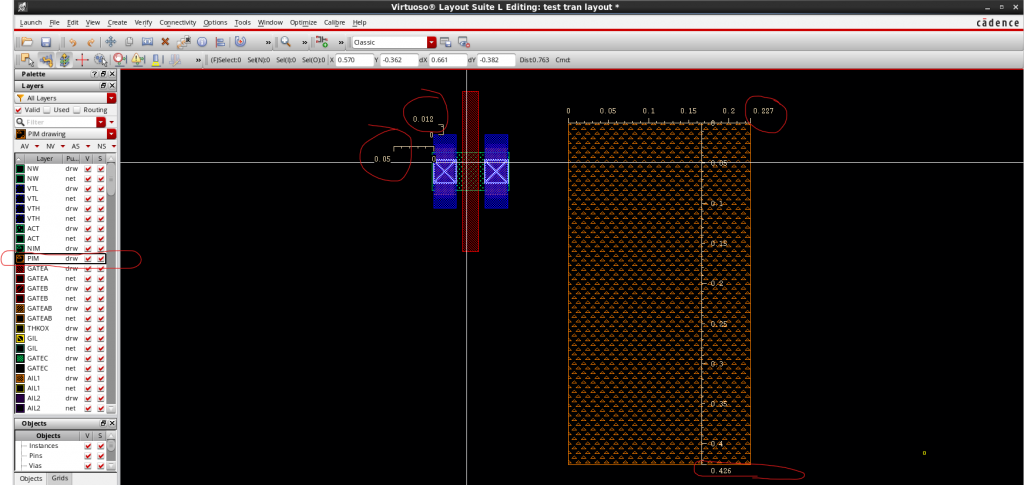

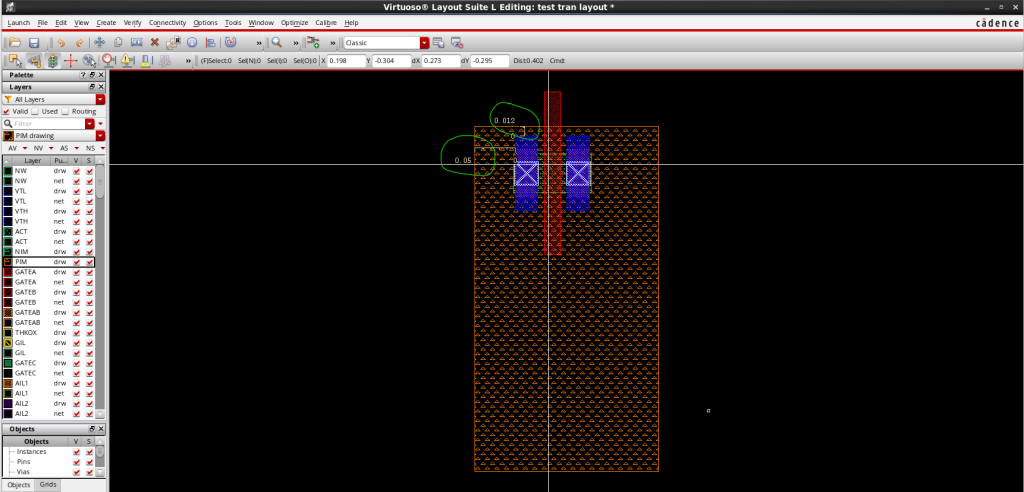

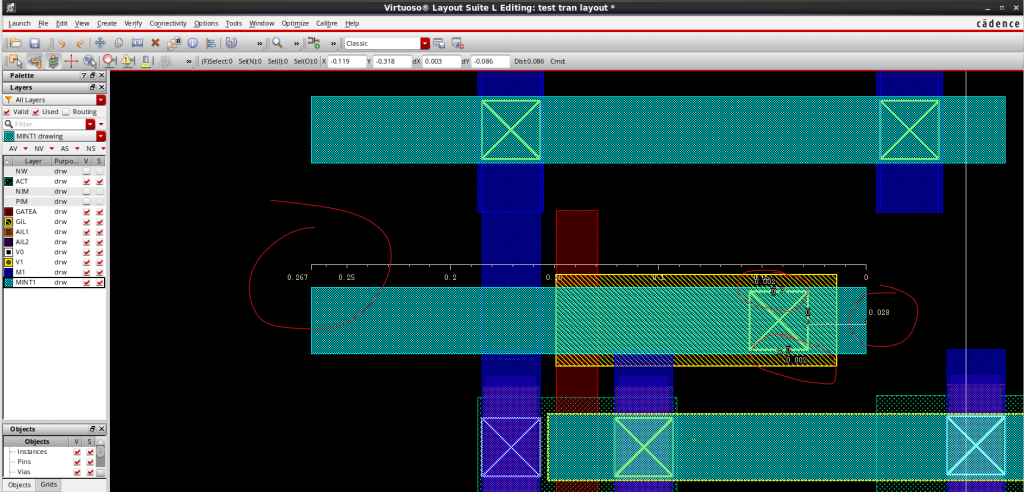

用 PIM Drw 绘制一个 227 nm * 426 nm 的矩形,这比规则文件所规定的最小面积大一点,当然你也可以不按照这个画。

画好之后,我们得将它移动有源区的下方,左端距离 M1 层 50 nm ,上端距离 M1 层 12 nm。

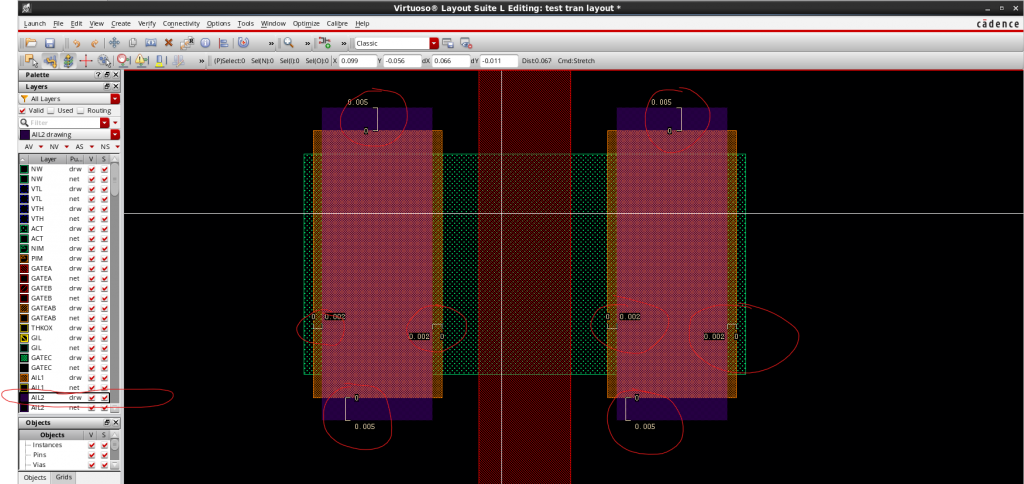

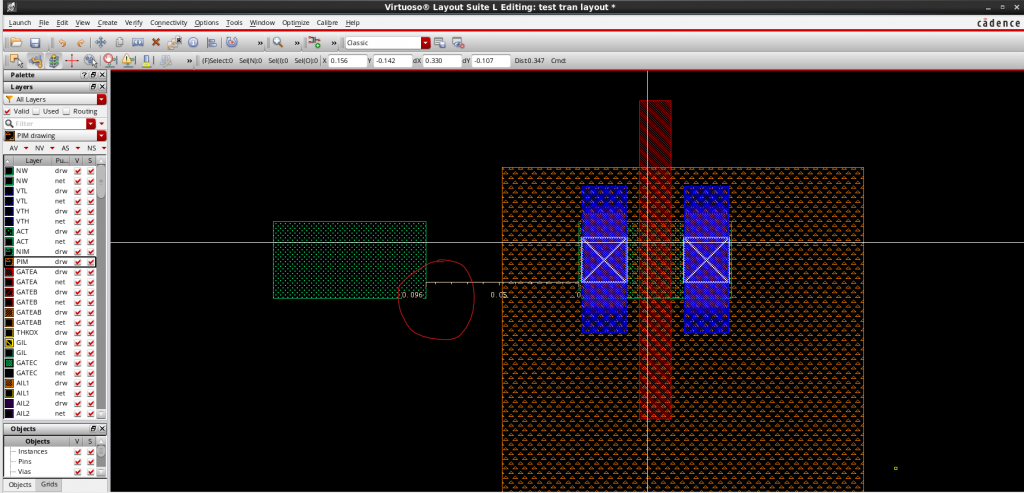

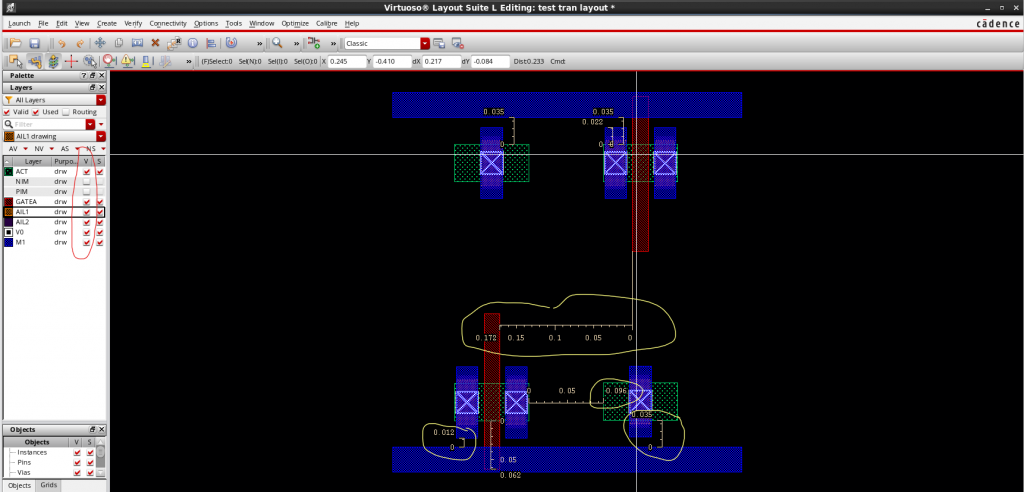

现在开始画与衬底接触,在有源区左边 96 nm 的地方做好标记,将原先的有源区复制到这里,小写 c 是复制,然后单击选择有源区可以进行拖动。

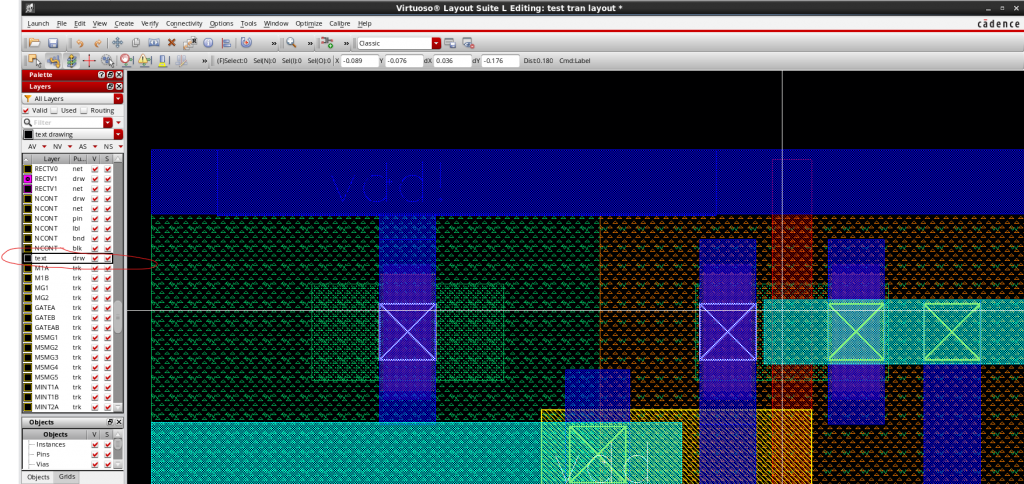

勾选下方的 Used , 可以查看当前使用过的图层,取消 v 下方的勾,可以隐藏当前图层。 在据左边有源层边缘 34 nm 的地方做好标记,按小写 c ,按住鼠标左键拖动,选择 AIL1、AIL2、M1 和 V0 层 。

松开鼠标左键,将选中的 4 个层拖动到左边有源层的标记处,使得 M1 层与 34 nm 处对齐。

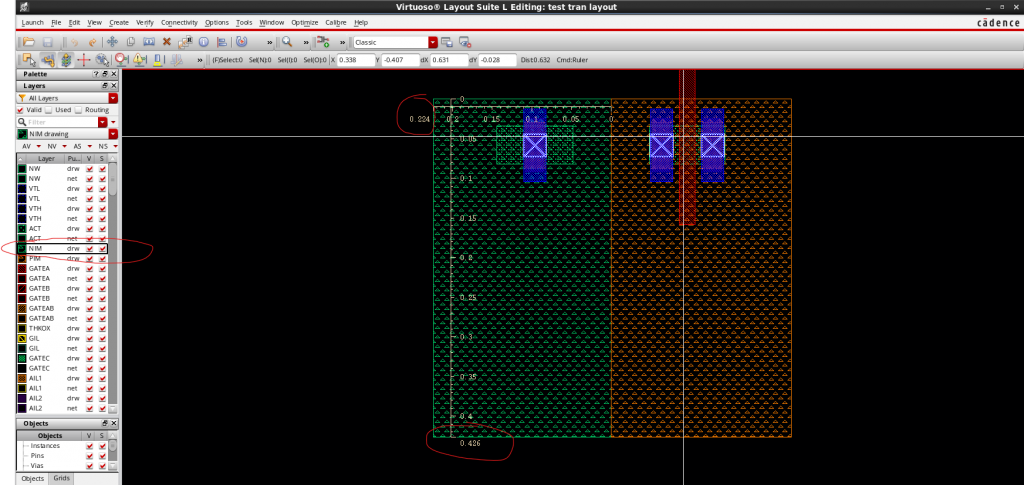

使用 NIM Drw 层绘制 224 nm * 426 nm 的矩形,高度与 PIM 层对齐。

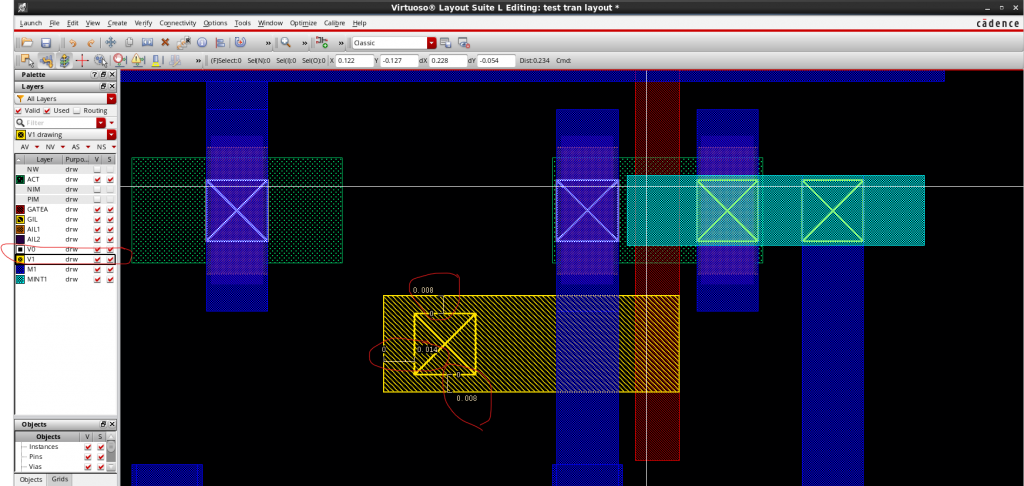

前面画的稍微有点错误,将下面两处稍微修改一下,首先, PIM 层据栅源为 13 nm,将 PIM 层将上移动 1 nm,同样,也将 NIM 层往上移动 1 nm,其次,将栅极往下移动,距离有源区(ACT)层 62 nm。

选择 M1 Drw 层,在距 PIM 层上方 32 nm 做好标记,绘制下面的矩形,左边跟 NIM 层对齐,右边跟 PIM 层对齐。

将画的复制一份,移动 PIM 和 NIM 层下面,如下图。

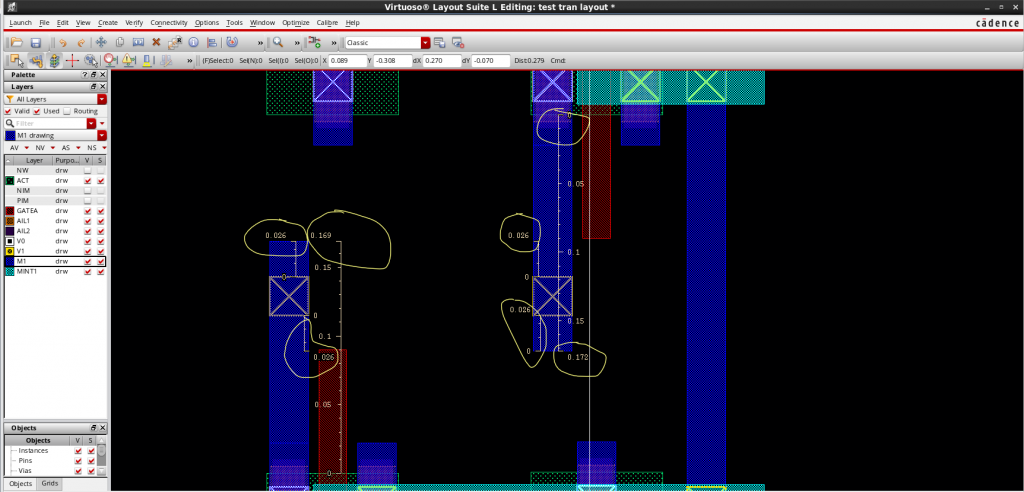

先将 NIM 与 PIM 取消显示,将与衬底的接触和有源区那部分复制,各个距离如图所示。

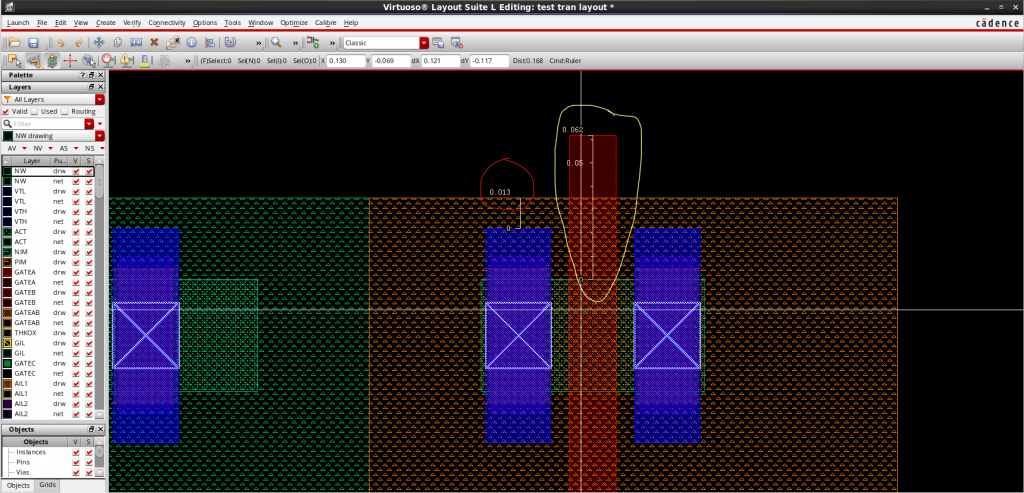

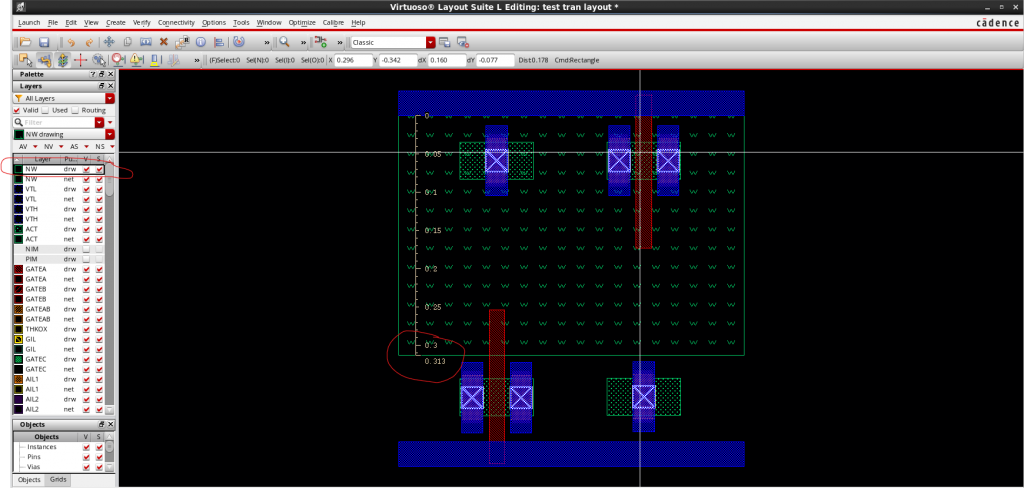

背景默认为 P 型衬底,NMOS 可以直接画在上面,PMOS 则不能,PMOS 的衬底为 N 型半导体,所有我们必须的画一层 N 阱(重掺杂),用 NW Drw 层画长为 451 nm,宽为 313 nm 的矩形,如下图所示。

这样,PMOS 和 NMOS 就算画完了,现在就是要进行连线了。现在用 MI Drw 层将 PMOS 的衬底与上面的 MI 层相连,NMOS 的彻底与下面的 M1 层相连,如下图所示。

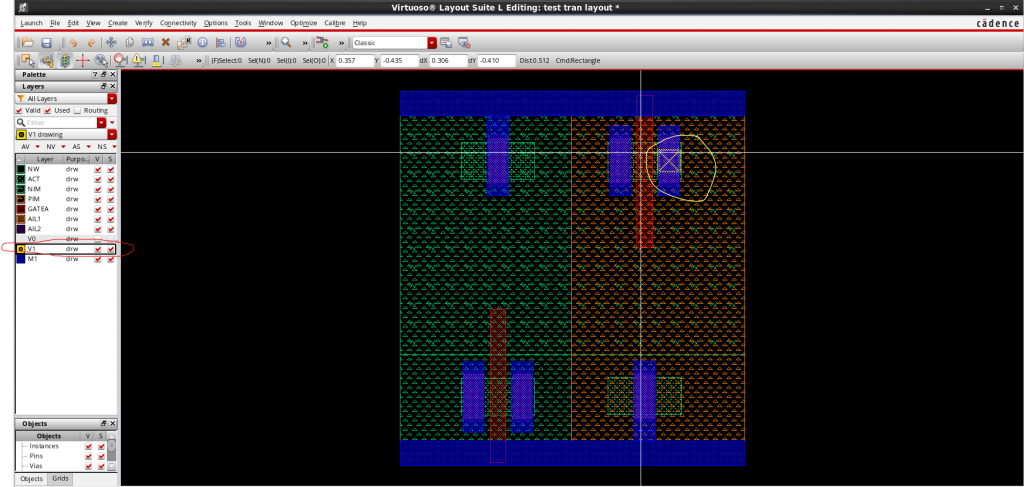

用 V1 Drw 层(连接金属 1 和金属 2 的)在 V0 的上方画一个宽长一样的矩形,如下图。

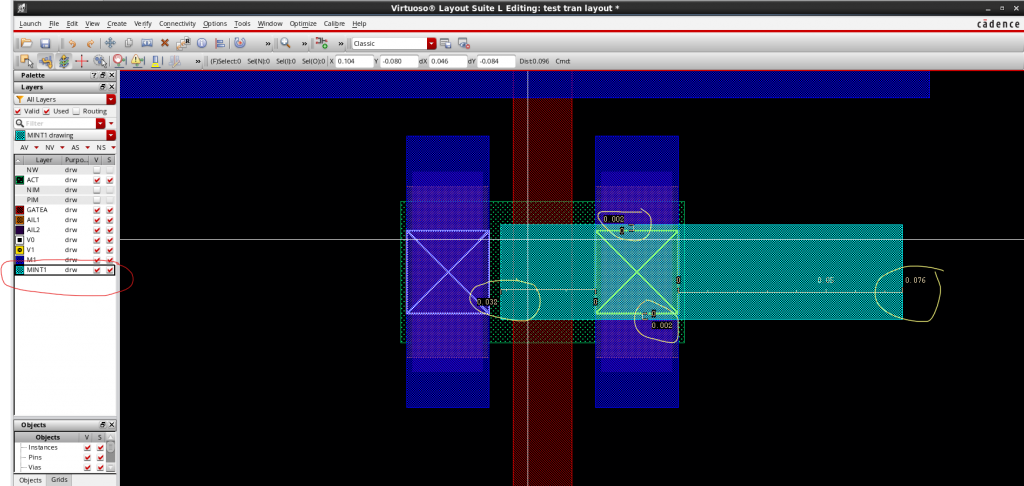

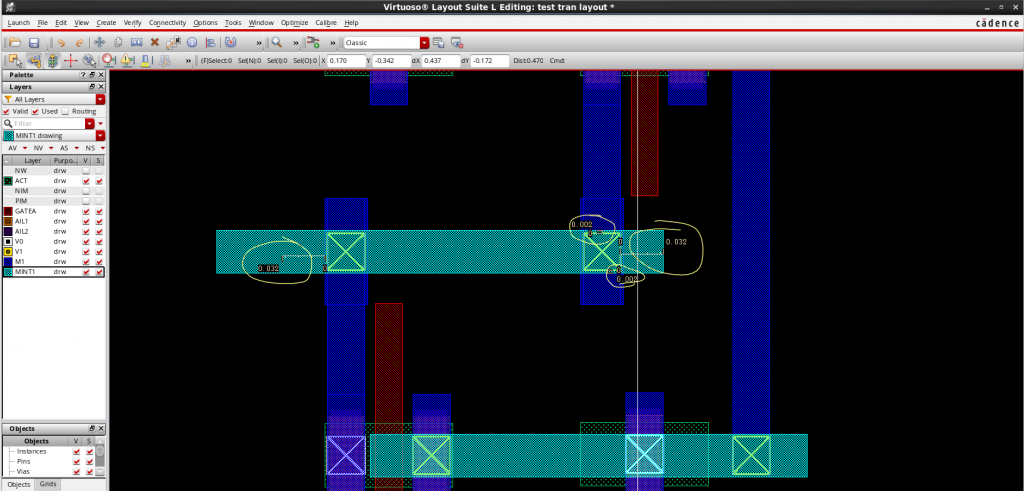

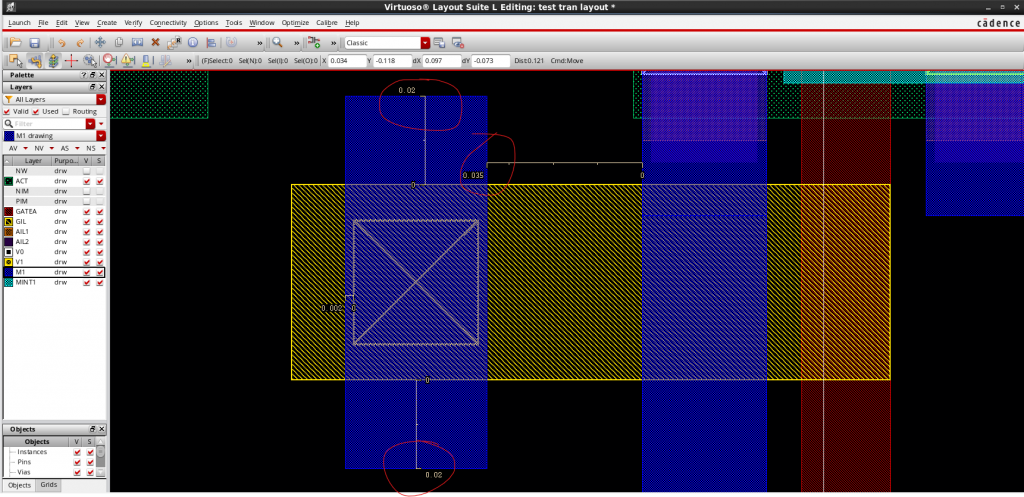

在 V1 上面 2 nm 的地方做好标记,左 32 nm ,右 76 nm,用 MINT1 Drw 层画矩形,同样,MINT1A 和 MINT1B 都是金属 2 层,只是用了不同的颜色和填充表示,drc 验证时也不会验证。

同样,在下面源漏地方用 V1 Drw 画一个孔,用 MINT1 Drw 层画一个长为 328 nm,宽为 32 nm 的矩形,矩形左边出头 32 nm,上下出头 2 nm。中间与衬底的接触看着跟 M1 层连接在一块了,由于没有在这个地方没有打孔(没有用 V1 层绘制),实际是没有连接在一块儿的。

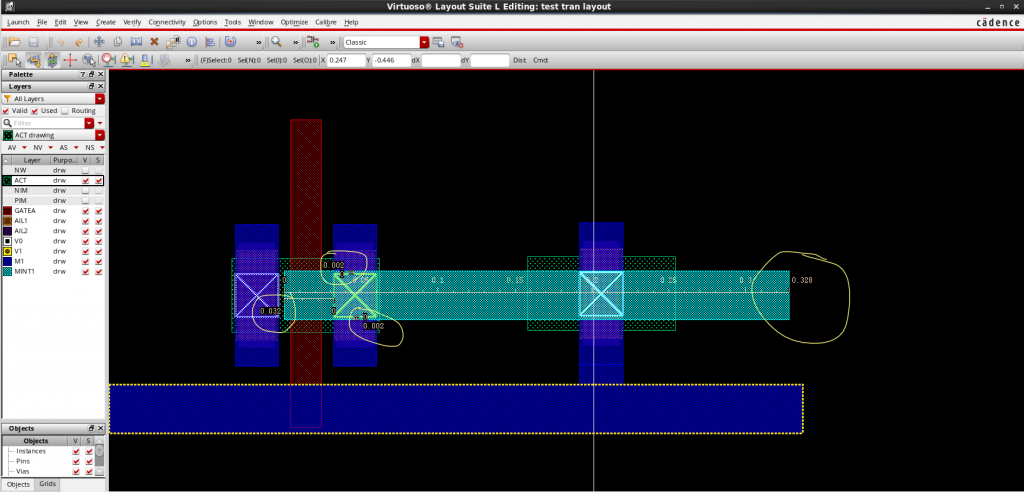

将用 V1 层画的孔复制,距离有源区 18 nm,下面也复制一个,用 M1 Drw(线宽为28 nm)层连接,两头与 MINT1 层对齐。

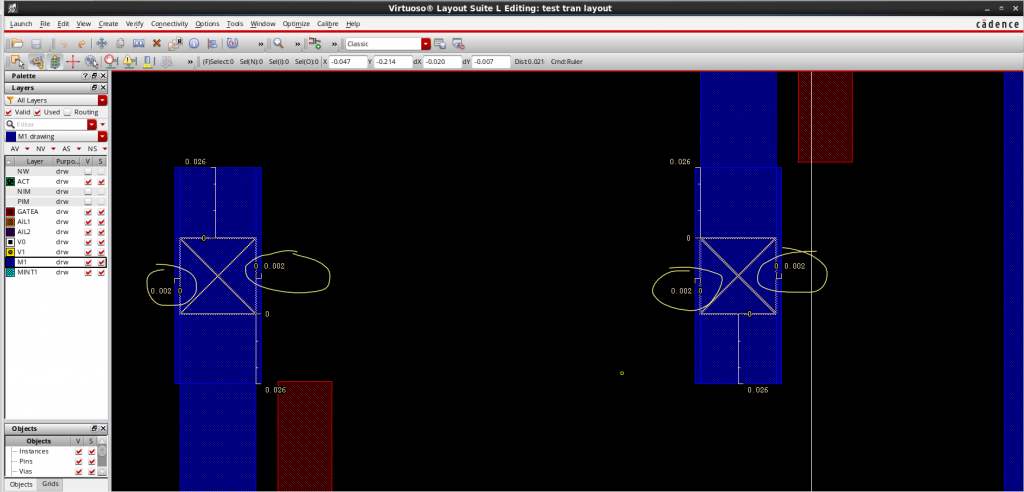

这样,PMOS 的漏跟漏就连接在一起了,MOS 管的源漏是可以互换的,因此你说这是源跟漏连接在一起了也是可以的,或者说这只是 PMOS 与 NMOS 有一端相连了。在这里,我按照左边是源,右边是漏进行连线。然后将源跟源相连。先将源延长,距离如下图所示,这里之所以要标记 26 nm 的地方,是因为我们需要对这个局部进行加宽以使得满足设计规则。

将左右各加宽 2 nm ,方法就是用 M1 层重新画宽一点。

然后用 MINT1 画矩形,左端要超过 32 nm ,因为后面还要在这儿加端口、标签这些。我这里将整个连线的长修改为了 334 nm 。

然后用 GIL Drw 层画一个 44 nm * 135 nm 的矩形,位置如下图所示。

在下方位置处,用 V0 和 V1 层画 28 nm * 28 nm 的孔,这两个孔是重叠在一起的,当然更方便的方法是直接复制画好的孔,拖动到图中位置。如果需要流片的话,并不建议这样画,而且孔最好不要只弄一个,这样的话由于实际加工,很有可能造成孔的质量不好,影响性能。

用 M1 层在图中位置画一个矩形。

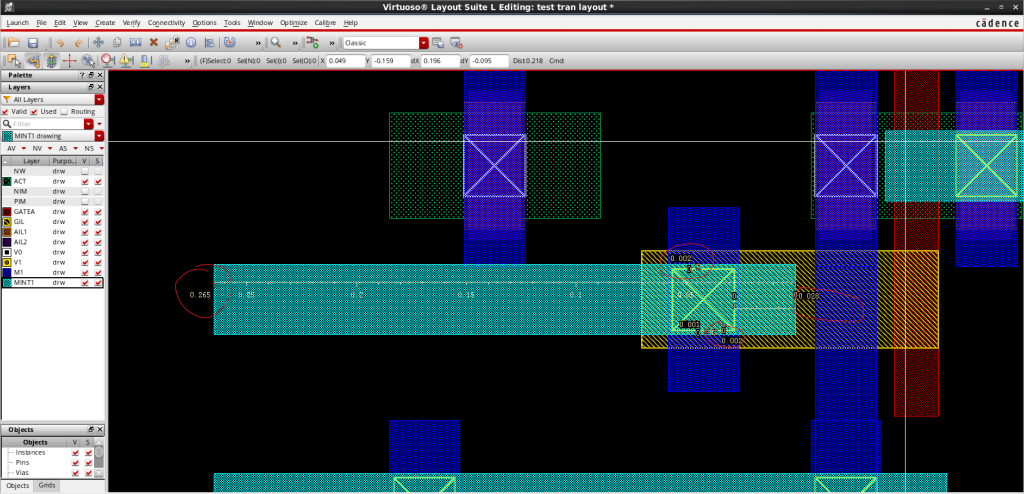

用 MINT1 绘制 265 nm * 32 nm 的矩形。

利用同样的方法,将下面 NMOS 的栅极也引出来。

这里在右边三个红圈处少了一段 M1 的矩形,这是在后面进行 LVS 验证时才发现的。

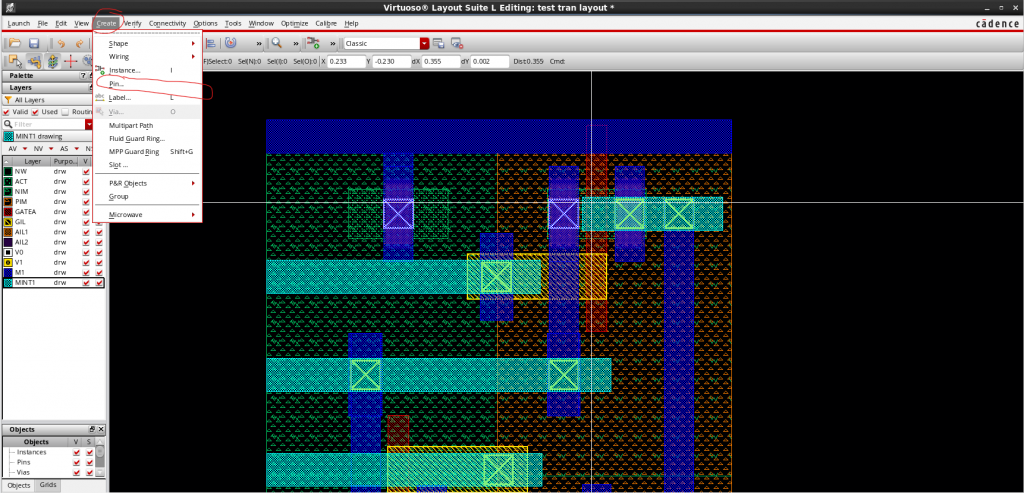

接下来就是画端口了。点击 Create — pin

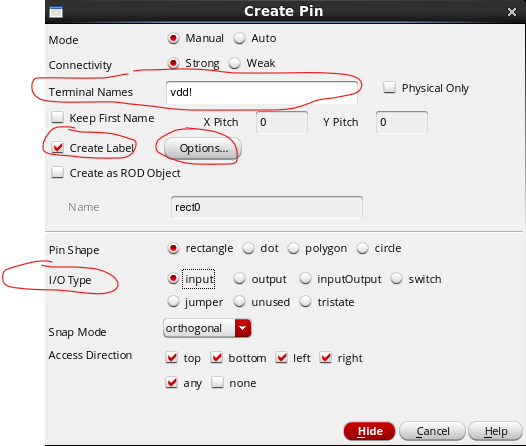

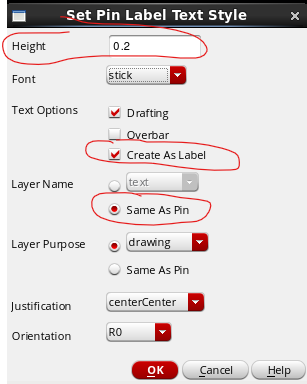

在 Terminal Names 中输入端口名字,注意:一定要和原理图中的端口名字一样,不然 lvs 通不过。勾选 Create Label,I/O Type 选择为 input ,点击 Create Label 旁边的 Options 。

Height 设置为 0.02(20 nm),勾选 Create As Label 和 Same As Pin 。

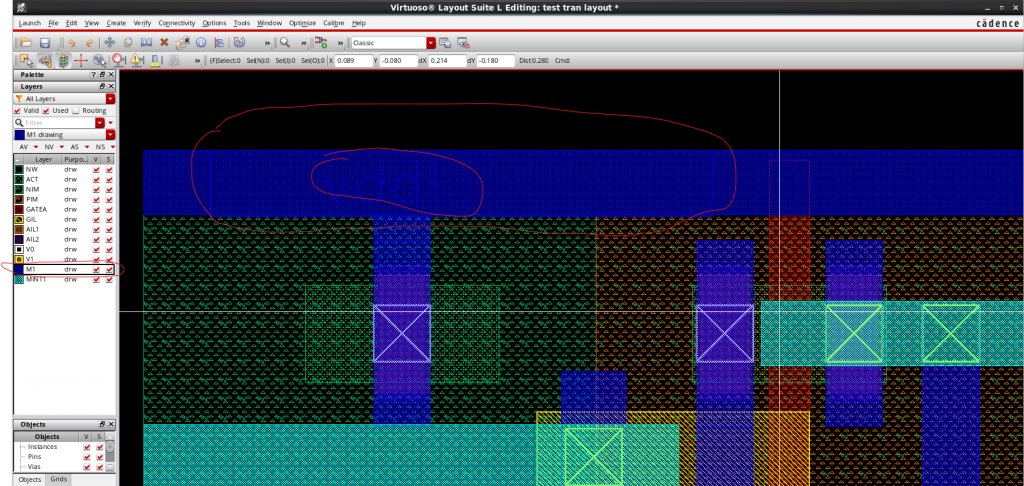

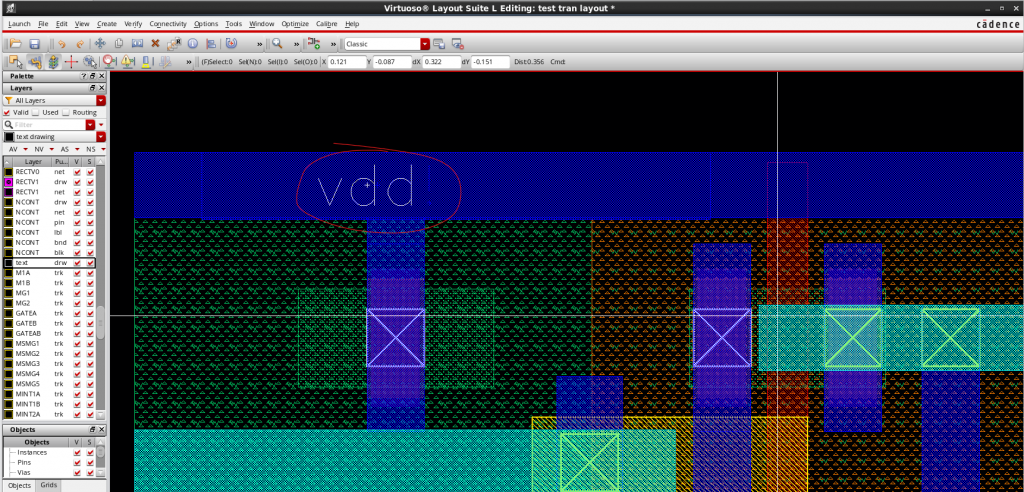

然后选择 M1 层,单击鼠标左键决定矩形的起点,再次点击鼠标左键决定矩形的终点,然后将 vdd 放在合适的位置。

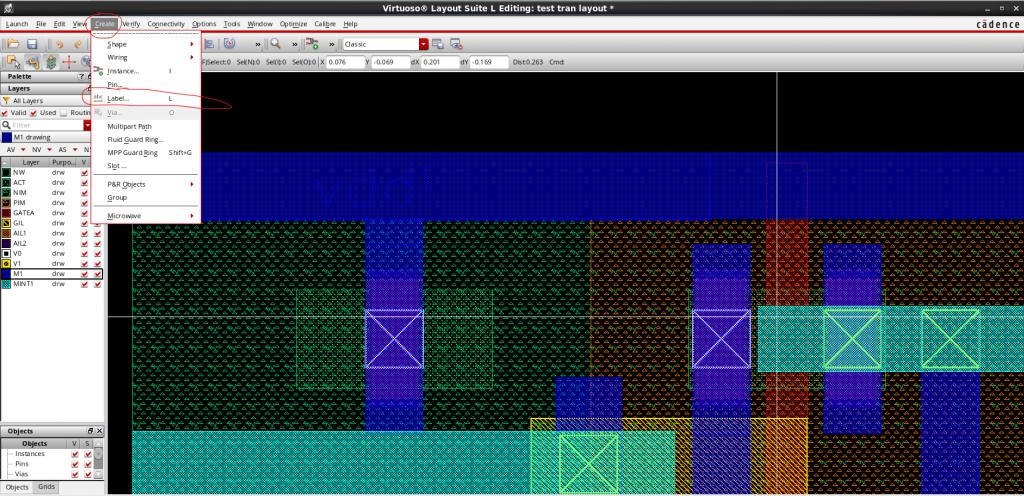

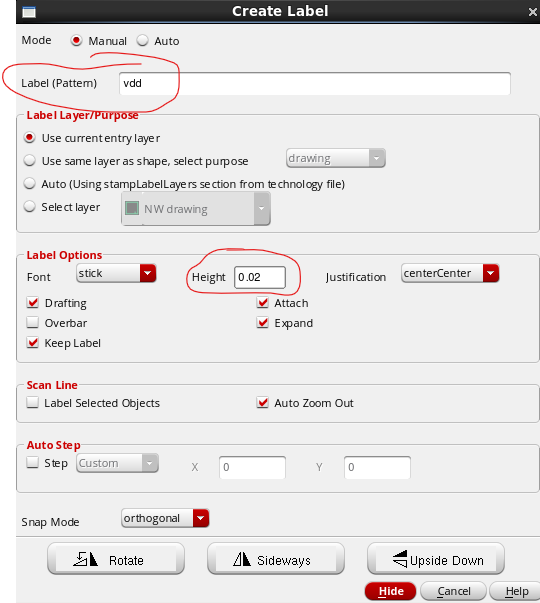

如上图所示,这样创建的 vdd 字样看不清除,我们可以点击 Create — Label 。

在 Label (Pattern)中填入 vdd (这个只是一个标签,可以任意填)。Height 设置为 0.02 。

然后选择 text Drw 层,放置 vdd 。

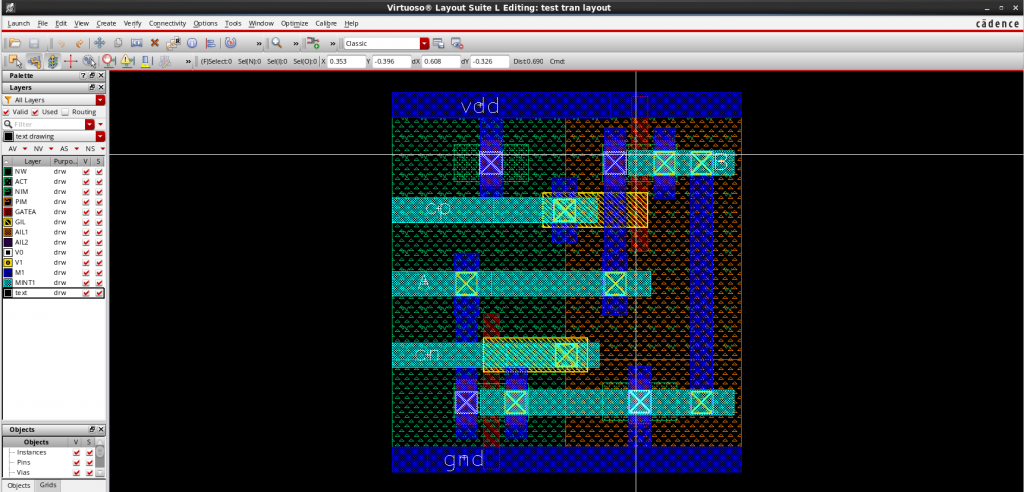

最终如下图所示

利用同样的方法添加 gnd、A、B、cn 和 cp,

gnd: Terminal Names -- gnd! , I/O Type -- input M1 层

A: Termimal Names -- A , I/O Type -- inputOutput MINT1 层

B: Terminal Names -- B , I/O Type -- inputOutput MINT1 层

cn: Terminal Names -- cn , I/O Type -- input MINT1 层

cp: Terminal Names -- cp , I/O Type -- input MINT1 层最终效果如下图所示。

感谢您的支持,请扫码打赏