cadence IC系列使用(2)原理图

环境

系统:redhat 6.5

cadence IC版本:IC617

库:FreePDK15

模型:PTM-MG 7nfet 7pfet

版图验证工具:calibre(mentor)

仿真工具:hspiceD(synopsys)

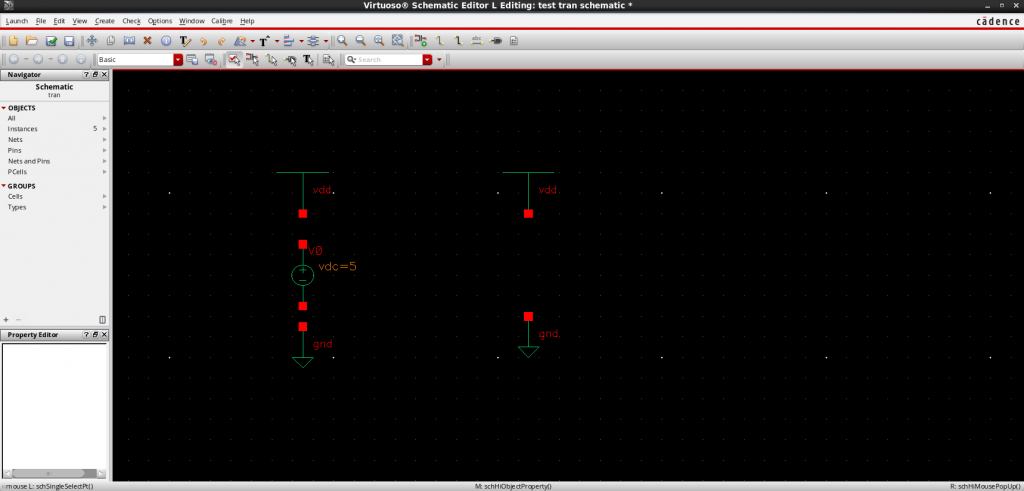

最终的原理图用来前仿的话可能会有点小问题,如果有问题的话,可以删掉 vdc 及与之相连的 vdd 和 gnd,如下图所示

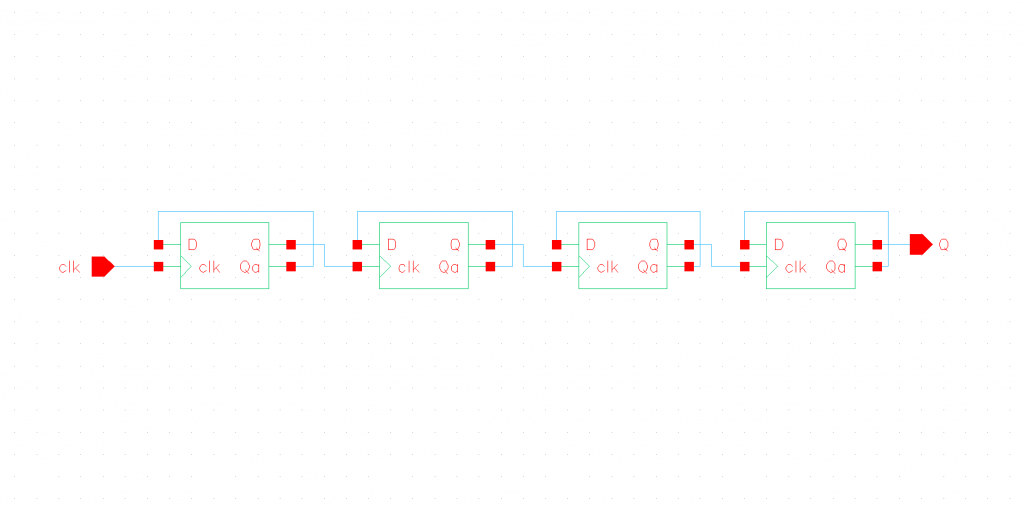

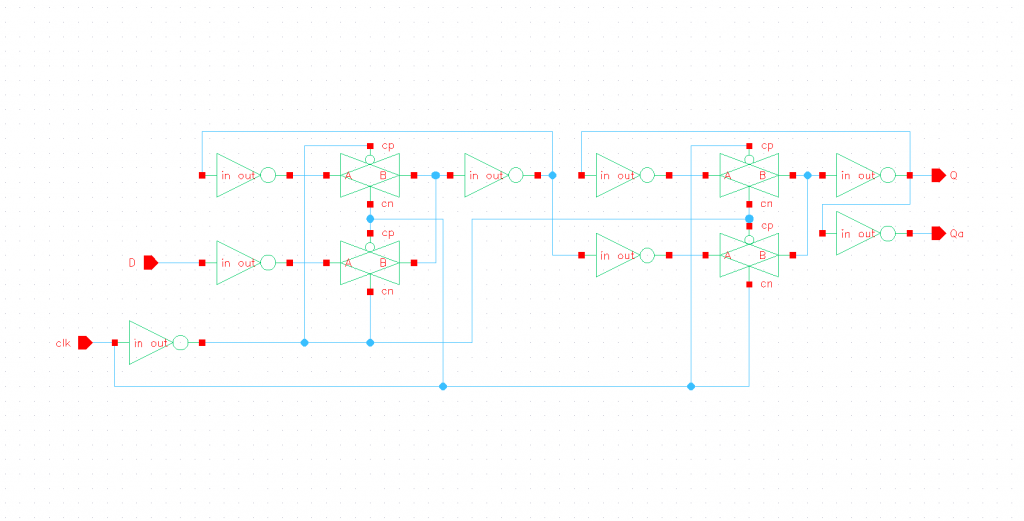

以16分频器为例,16分频起可以由4个D触发器构成,如下图所示

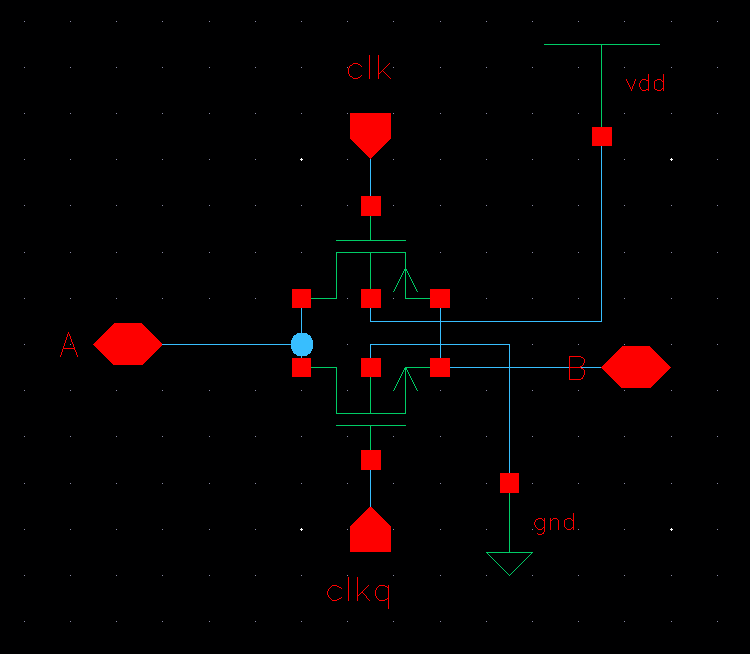

D触发器我采用的是用传输门和反相器构成的,如下图所示

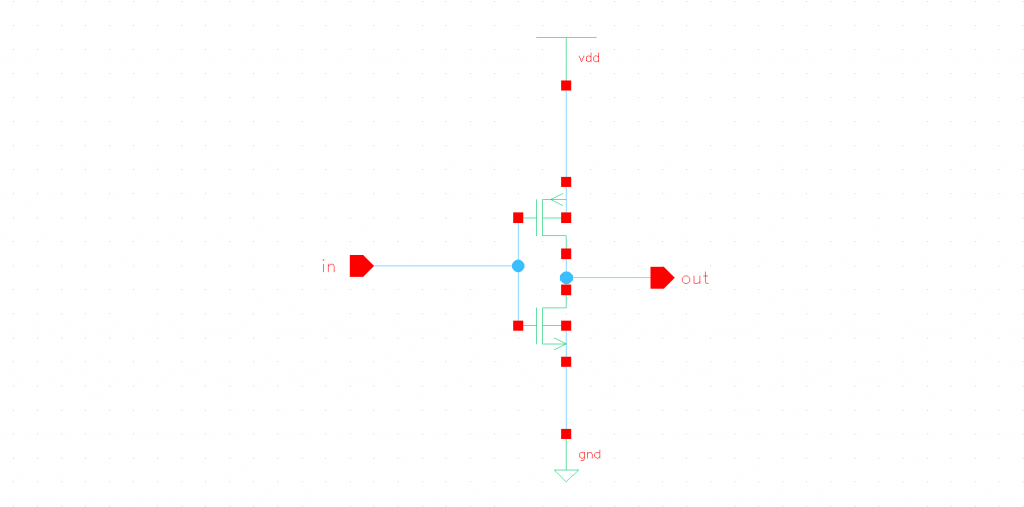

所以关键的步骤就是先画传输门和反相器,反向器的电路图如下所示

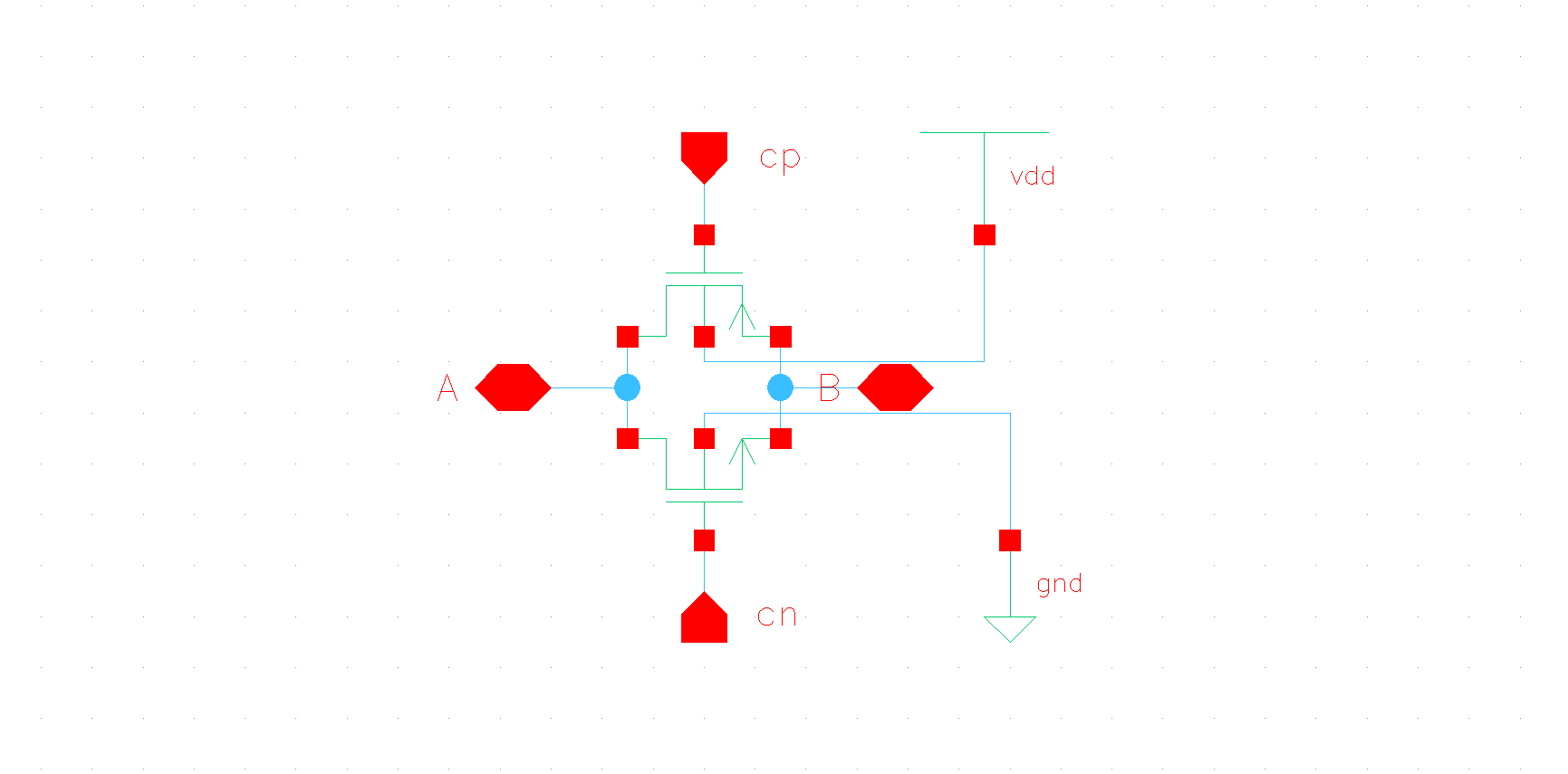

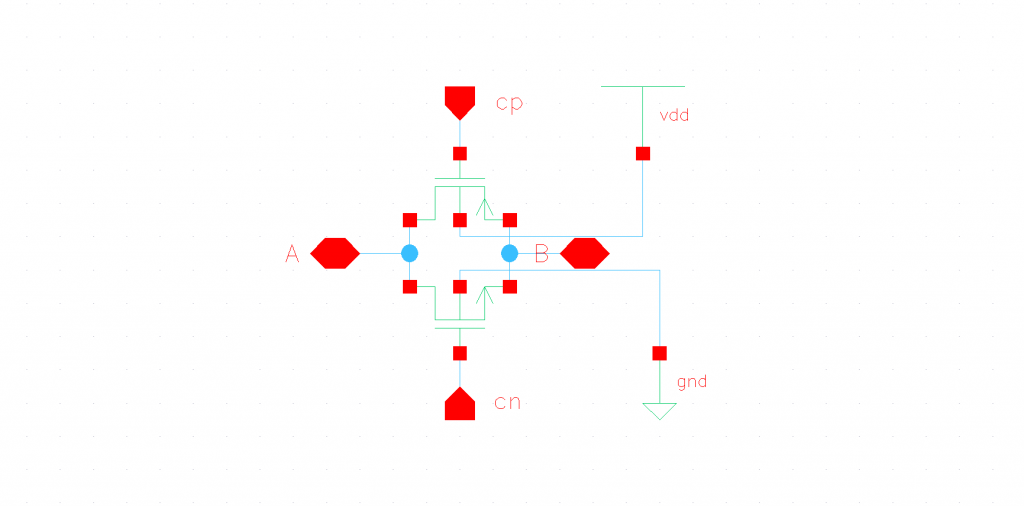

传输门的电路图如下

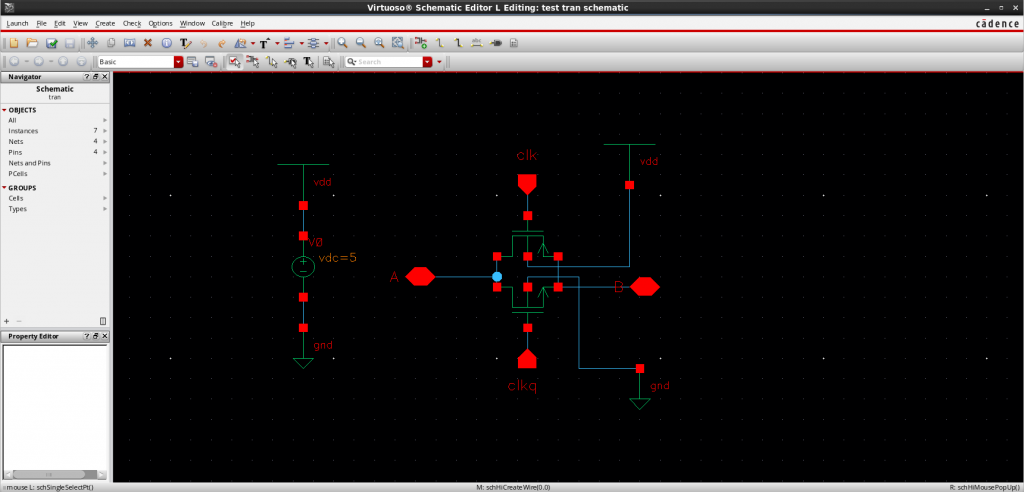

下面以传输门为例介绍一下,如何画原理图,封装成符号图(symbol图),画版图,验证,参数提取及后仿真。

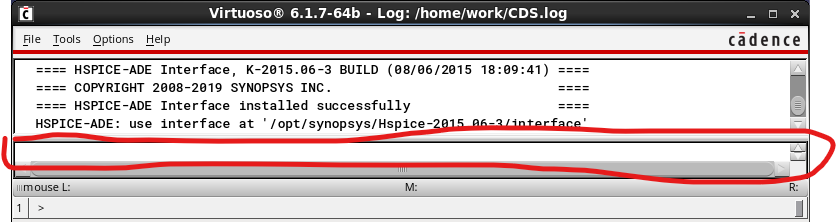

打开 cadence 软件,如果你用的是前面的虚拟机的话,打开 terminal,直接输入 virtuoso & 即可打开 cadence IC617,输入 ifcb & 即可打开51版本,这里的符号 & 表示在后台运行,懂一点 linux的人应该都知道,如果你是自己装的软件,则需要做一些设置,主要就是软件的位置,license 的路径等。输入命令后回车就会出现下面的 CIW 窗口,在中间那条白色的地方可以输入命令。

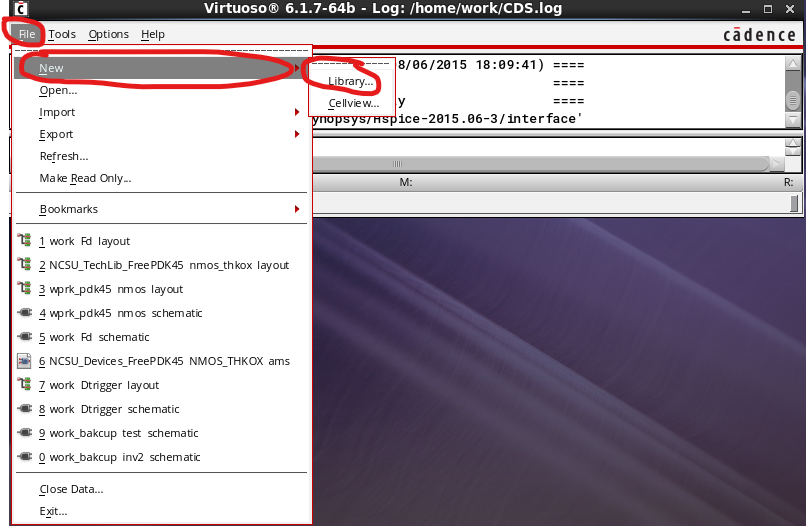

然后点击 File — New — Library

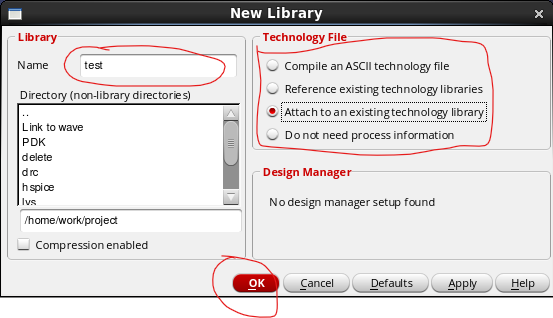

在 Name 中输入库的名字,这里用 test,右边有四个选项,第一个 Complie an ASCII technology file 是编译一个技术库文件(通常以 .tf 结尾,虽然 Linux 下后缀没任何意义),如果你只选择这个的话,后面画版图时所有图层全是一种颜色,并且如果你只有技术库文件的话,是没办法进行版图验证的。第二个Reference existing technology libraries 是参考一个已经存在的库,第三个Attach to an existing technology library 是连接到一个技术库,第四个 Do not need process information 是不需要任何处理。在这里,我选择的是第三个 Attach to an existing technology library

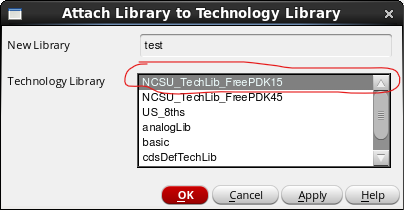

由于我用的是库是 FreePDK15,所以我选择的是 NCSU_TechLib_FreePDK15 ,这个库与其它你在网上见到的库有所不一样,主要是其它库所对应的工艺都是平面型 CMOS 工艺,而这个库所对应的 MOS 管叫做鳍式场效应晶体管,在后面画版图时就不能按照平面CMOS工艺画了。点击 OK 后,工作库就创建好了。

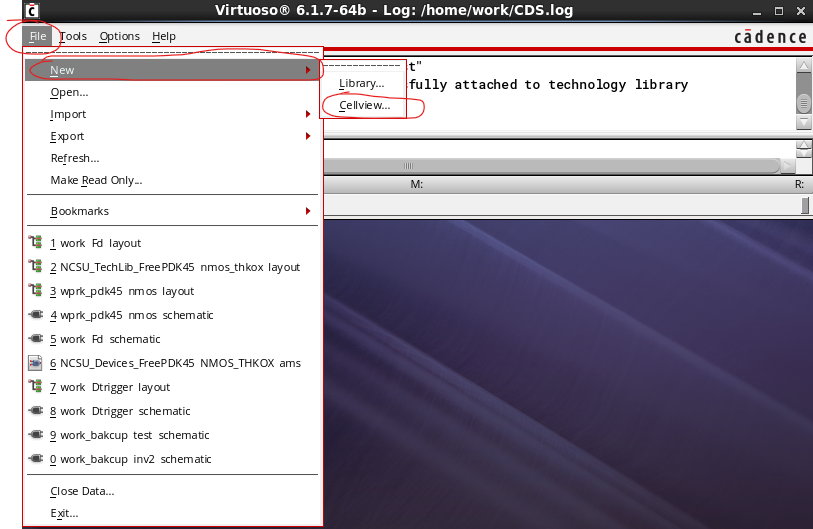

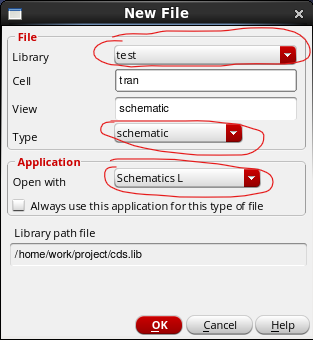

然后就是新建视图了,点击 File –– New— Cellview

在 Libraray 中选择我们新建的工作库 test ,如果你的库选择错了,原理图就在其它库中了,当然影响也不大,稍后复制或移动到这个库中就完了。Cell 名字随意,这里我取为 tran,Type 选择为schematic,选择Type后,View会自动发生变化,open with 选择Schematics L,然后点击OK

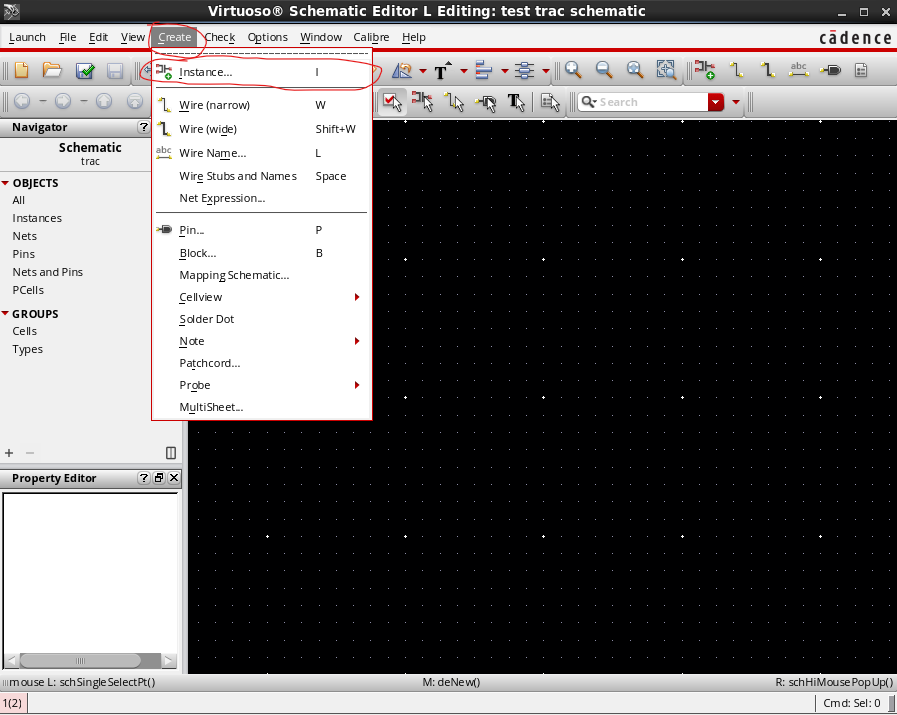

就会出现画原理图的窗口,点击 Create—Instance ,快捷键为小写的 i,这一个快捷键跟画版图的窗口中是一样的,但是其它快捷键在画版图的窗口就不一定可以用了。

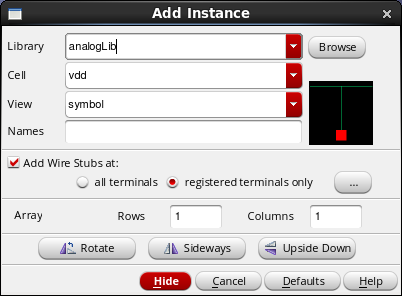

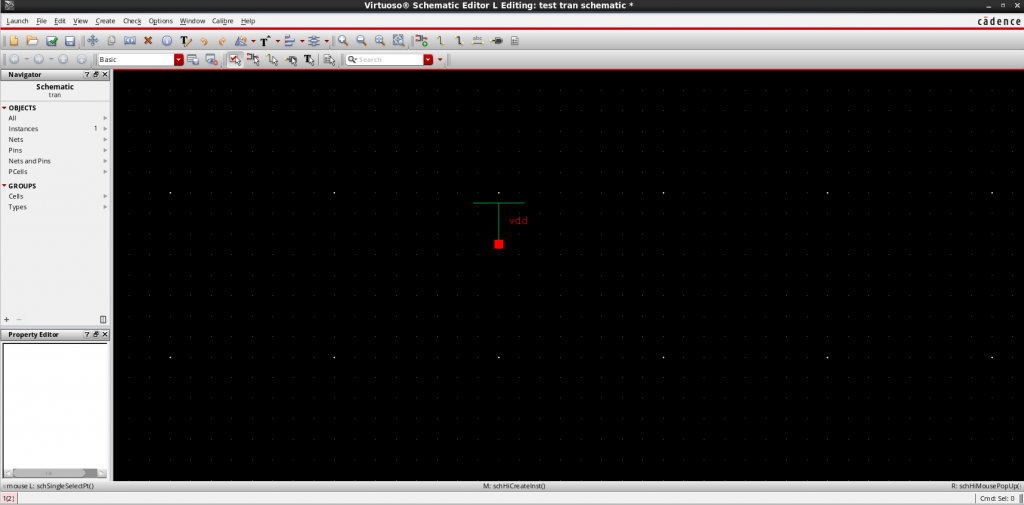

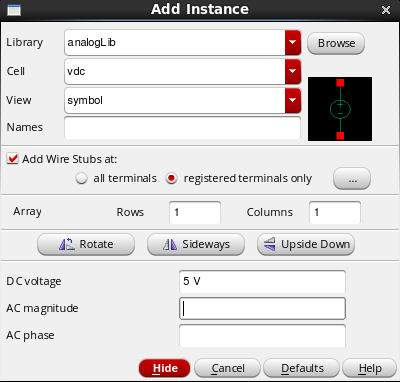

然后就会出现弹出下面的框,在 Library 中选择 analogLib ,这是一个模拟器件库,里面包含了各种器件,在 Cell 中先选择 vdd ,View 中选择 symbol ,在上面黑色框框中点一下即可放置电源 vdd,在放置的过程中可以按鼠标中键(有时按鼠标中键是重复上一个命令,不知道是不是跟软件配置文件有关)实现旋转,用同样的方法添加 GND,需要注意的是:GND电压默认为0V,vdd却没有默认值,也就是说,如果vdd为5V,你必须在vdd和GND之间加一个5V的电压。如果图像太偏了,可以按住鼠标中键拖动整个图形(好多CAD软件鼠标中键默认都是拖动图形,如Autodesk CAD)和鼠标滚轮放大缩小图形,或者单击菜单栏下的 View — Zoom To Fit,快捷键是大写的 F(shift + f)缩放到适合编辑的大小和位置。

用同样的方法添加 gnd, vdc ,在添加 vdc 时可以将电压改为 5 0.7 v。注意:在DC voltage中只需要填写 5 0.7 即可,软件会自动添加单位“V” (因为这个管子的工作电压只需要 0.7v 就够了)。

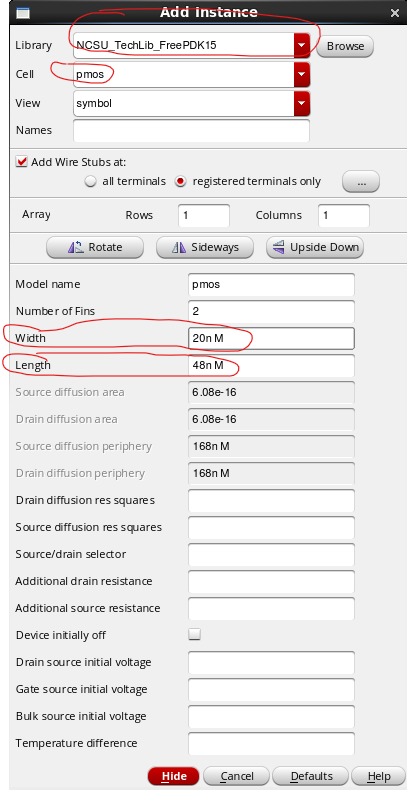

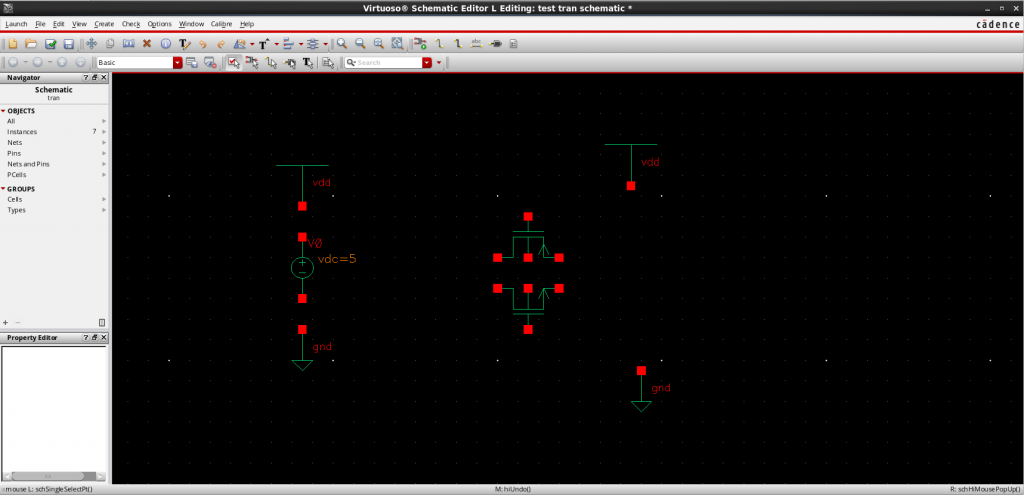

然后是添加NMOS和PMOS,这里需要选择的库是 FreePDK15,Cell 选择 pmos,需要改变下面的 Witdh 和 length (其实对于鳍式场效应晶体管来说,宽长已经不是那么重要了,不像0.6um工艺或者45nm工艺,鳍式场效应晶体管宽长本来就很小了,因为都是标准工艺,就算你改大或者小一点,也不一定可以加工出来,更重要的其实是鳍的数量),这里我们设置为 20 nm 和 48 nm,这是当前工艺库的极限。同样,这里只需要输入 20n 和 48n 即可,默认单位为 m。这里沟道的宽和长需要跟后面画的版图中的沟道宽长一致,不然 lvs 不会通过。利用同样的方法添加 NMOS,有些库里面 PMOS 和 NMOS 是三个脚的,这是因为它们的衬底默认是接了地(NMOS)或者电源(PMOS)的。比如在 analogLib 库中,nmos4对应的才是四脚。

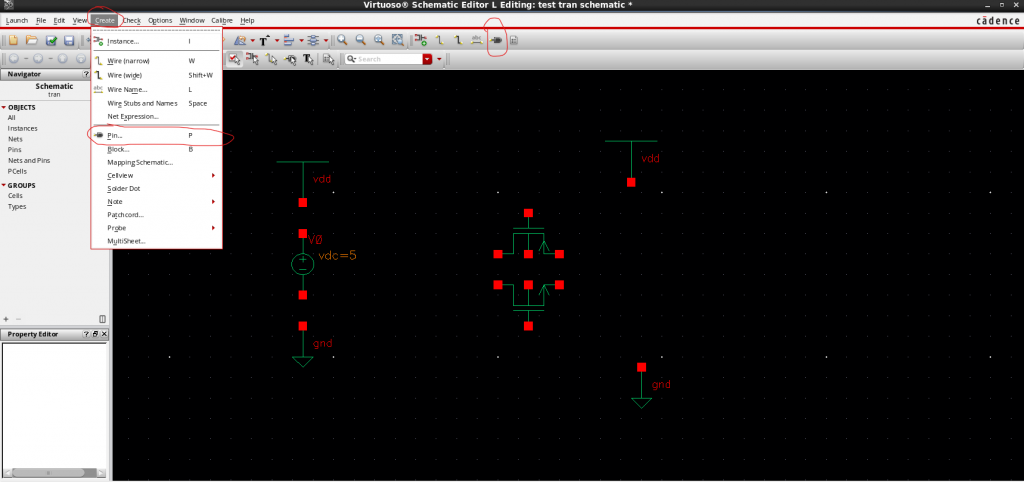

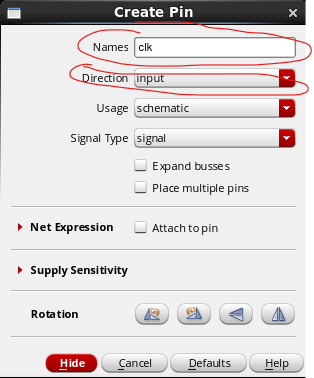

然后添加端口,点击 Create–Pin,或者点击菜单栏下方引脚的标识(图中已圈出),快捷键为小写 p

Names 可以随便写,区分大小写,但是别写成 vdd!,gnd!,它们是全局电源和地,后面版图添加端口时也需要跟这个一致。Direction 选择 input,如果端口方向不是很好看,可以按小写 r, 然后点击需要旋转的对象,即可旋转。利用同样的方法,添加三个端口,分别为 clkq — input , A — inputOutput ,B — inputOutput 。快捷键小写 c 是复制,小写 m 是移动,小写 u 是撤销(保存了就不能撤销)。

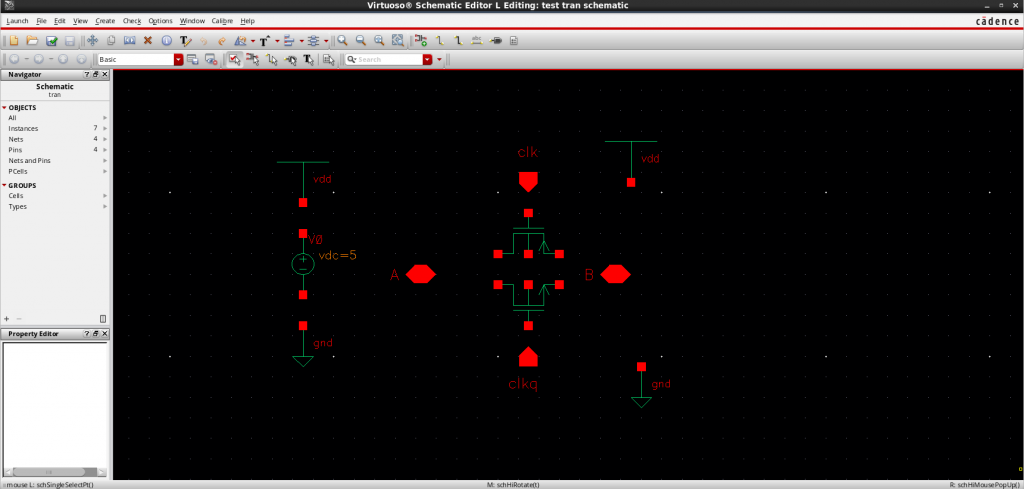

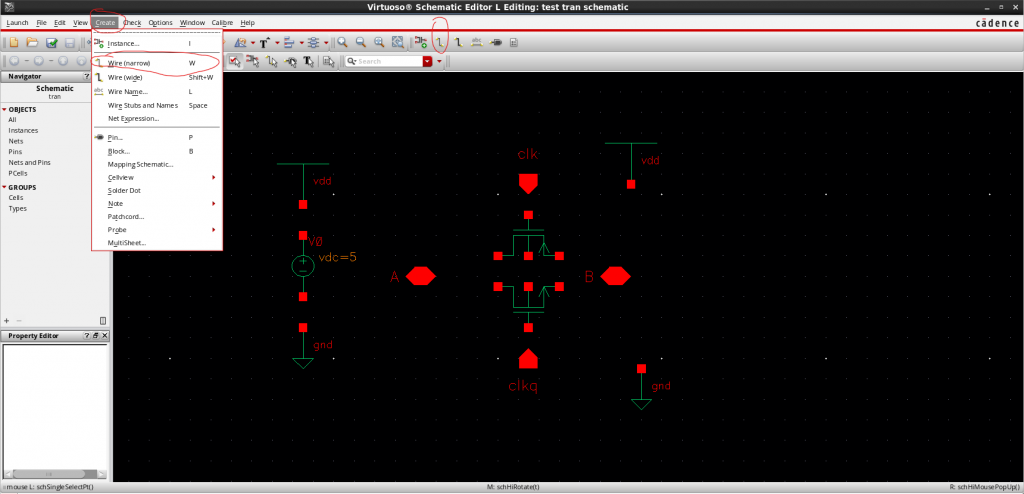

接下来需要做的就是连线了,点击 Create–Wire(narrow) 或者在菜单栏下方细线的标识(图中已经圈出来了) 或者按快捷键为小写 w 。

按照图示连线,小写 s 是保存(保存后就不能撤销了)

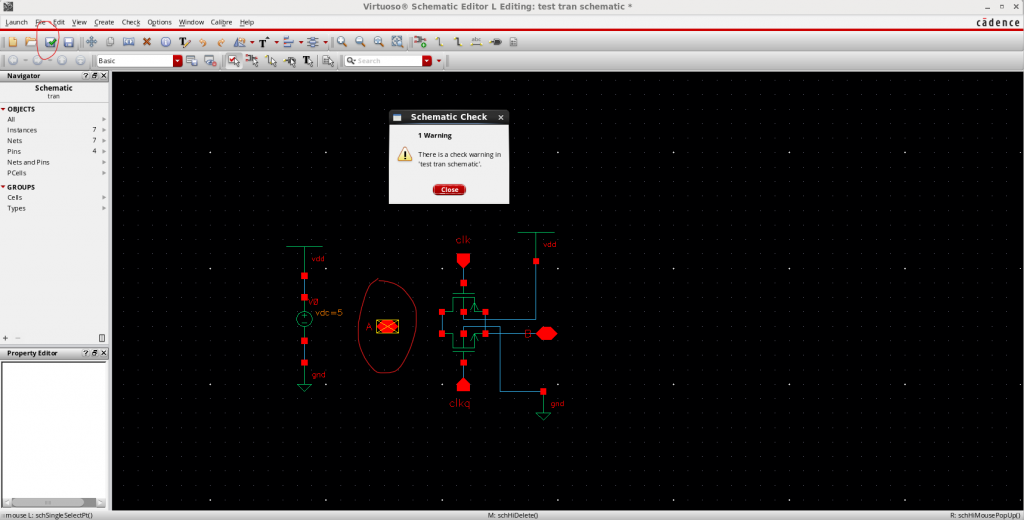

保存图标旁边那个保存中有一个绿色的勾的是保存并检查,包括检查是否有悬置的端口,没有连接号的线等,比如,故意去掉一跟线,如下图所示。点击保存并检查时就会出现一个警告,并在原理图中以高亮显示出来。

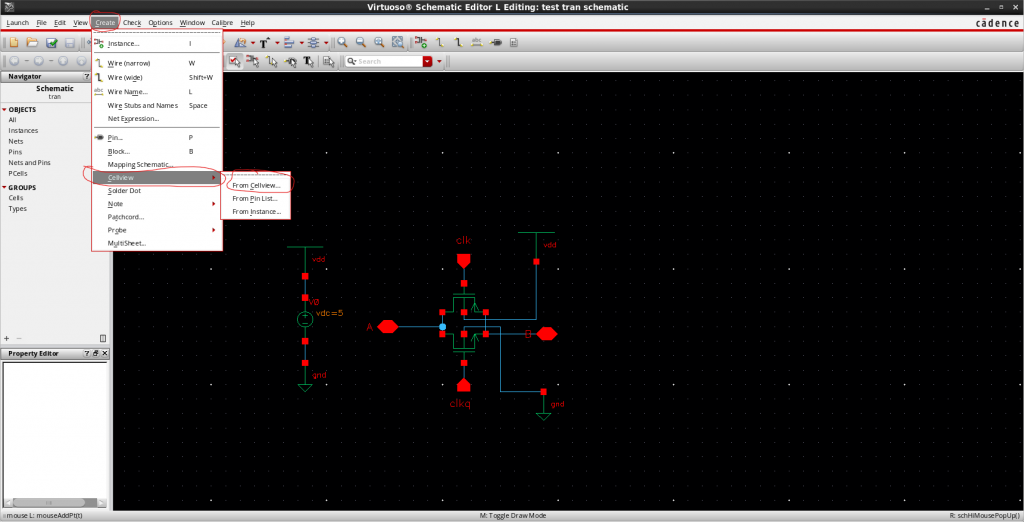

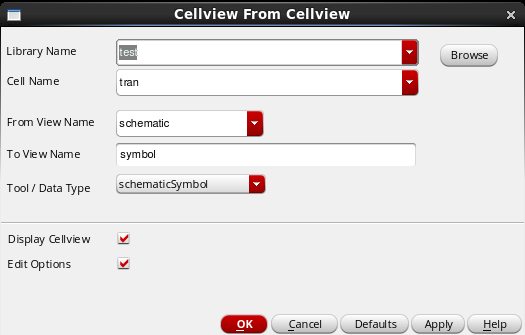

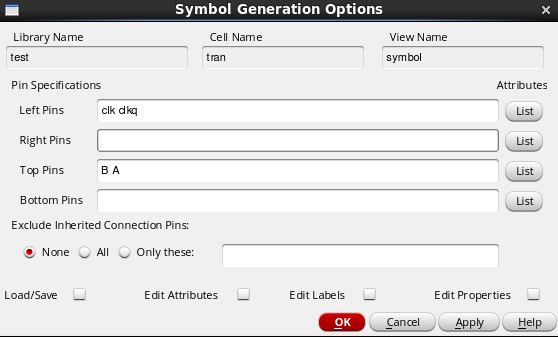

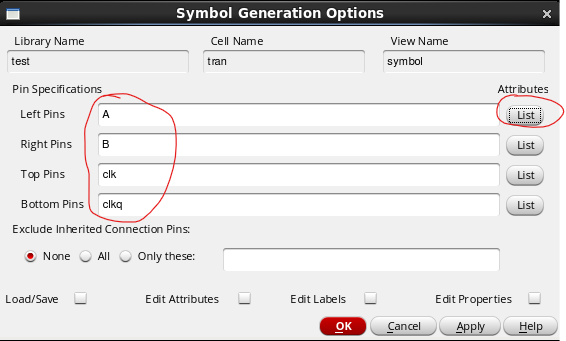

下面将原理图封装成 symbol 图,这样下次在原理图中就可以直接调用这个了,而不用重新在画一遍。选择 create — Cellview — from cellview 。

直接点击 OK 即可

出现下面的界面

为了使得符号图更好看,我们可能需要更改一下端口的位置(虽然在后面也可以改),如下图所示,右边的 List 可以修改端口的方向,然后点击 OK 确认。

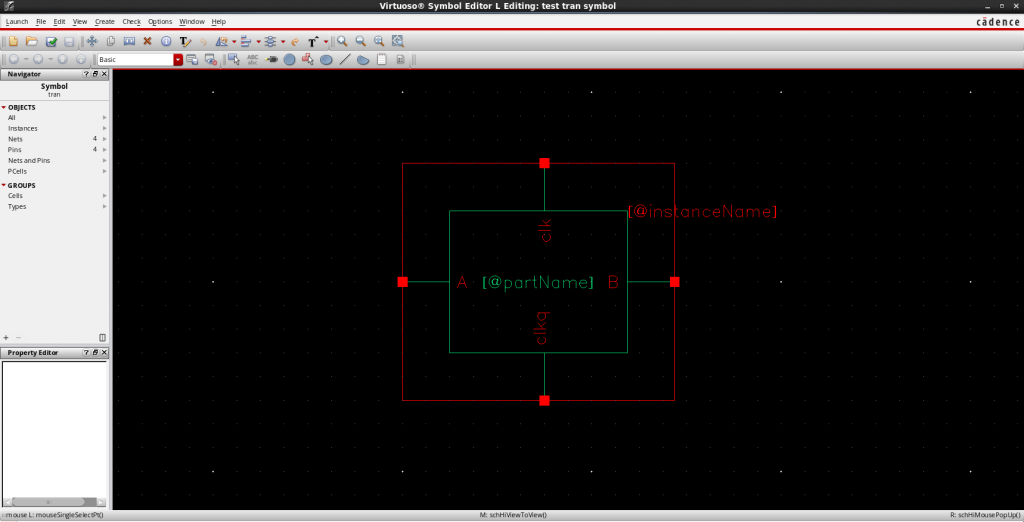

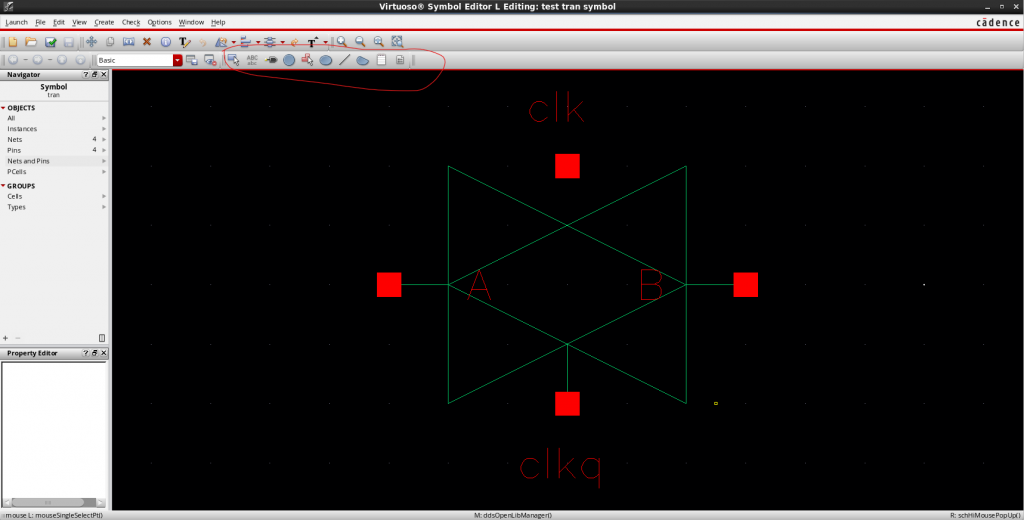

这样,一个symbol图就创建好了

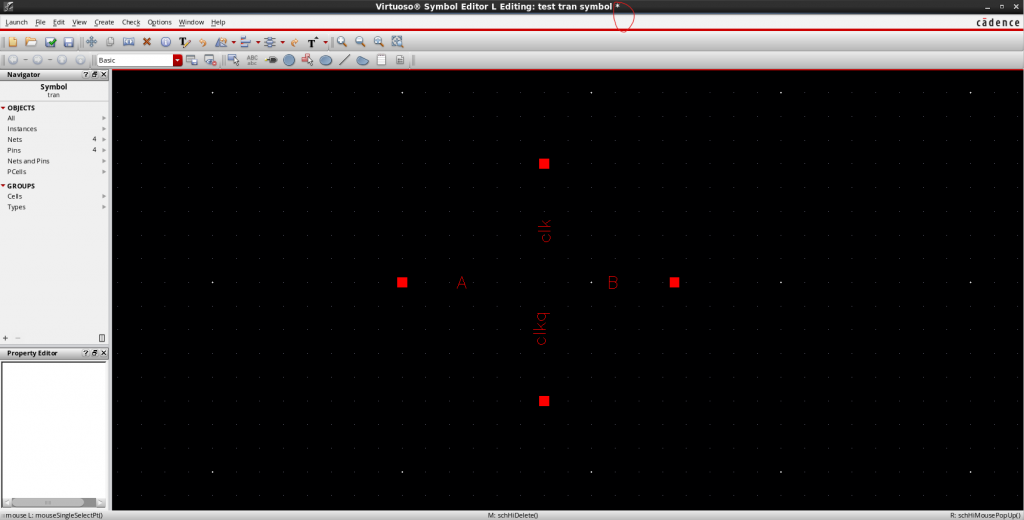

为了与电路中的符号图相对应,我们可以稍作修改,先删掉所有的线和字母,如果你是先选中线,再按 delete 键的话,就只能一次一次的重复,如果先按 delete 键,则可以一直重复这个动作,直到按 Esc 键取消这个命令。在标题栏中间,我们注意到有一个 * 号,这表示当前状态没有保存,在其它好多软件也是这样,如notepad。

选择字母(A,B,clk,clkq),按住鼠标左键可以只拖动字母,选择红色小框框,按住鼠标左键,则红框框跟字母会一起移动。下图中红色部分框起来的是绘图命令,先用直线画出下面的形状,画直线结束是双击,不是单击,单击是画折线。

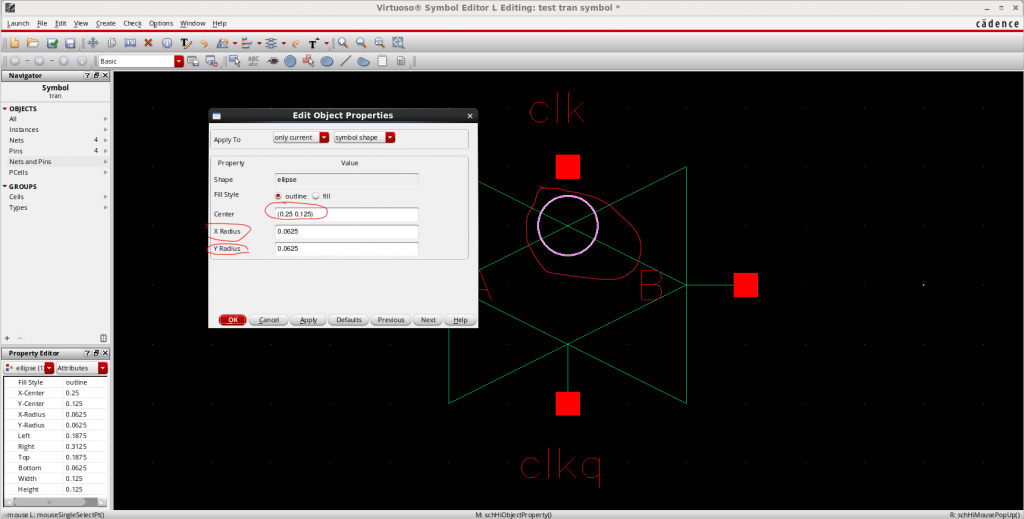

然后画一个圆,很明显,这个圆有点大,这是跟软件配置文件有关的,可以设置最短的捕捉距离来改变,或者点击,选中圆,按小写的 q 键,可以更改圆的属性。

修改圆心和半径,如下图所示。

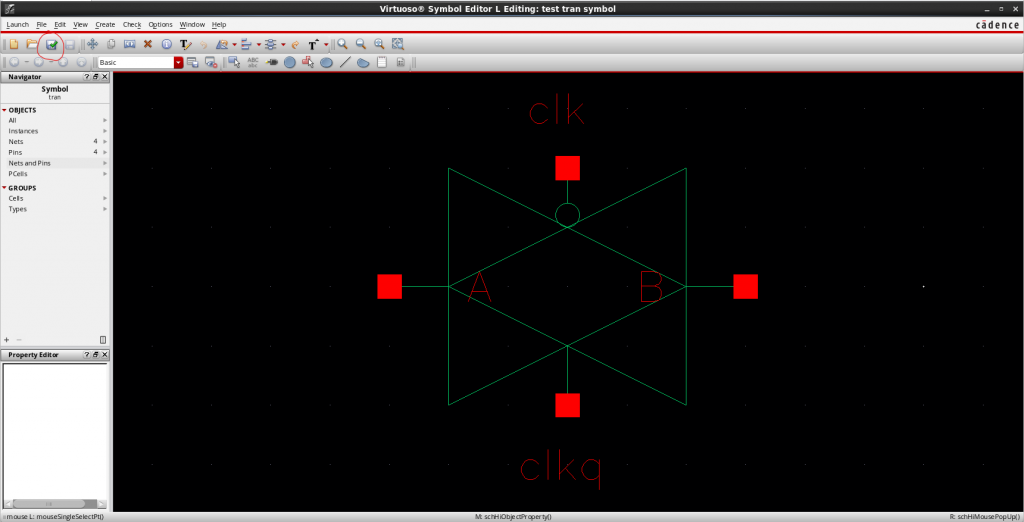

然后,连接圆与端口即可,如捕捉不到圆上,也可以修改线的属性。最后点击 保存和检查

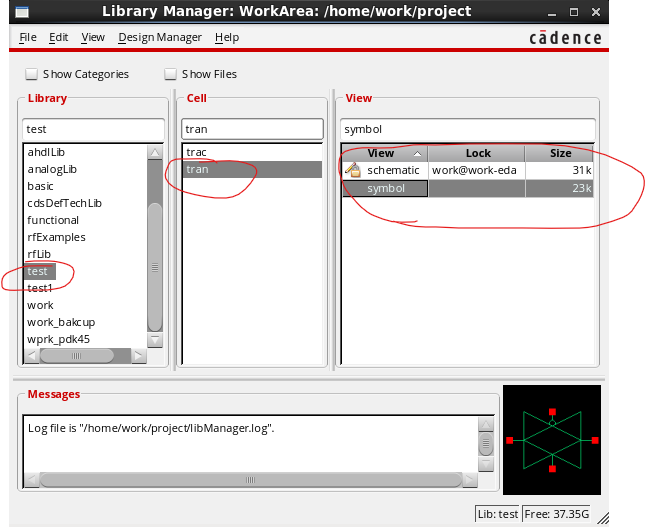

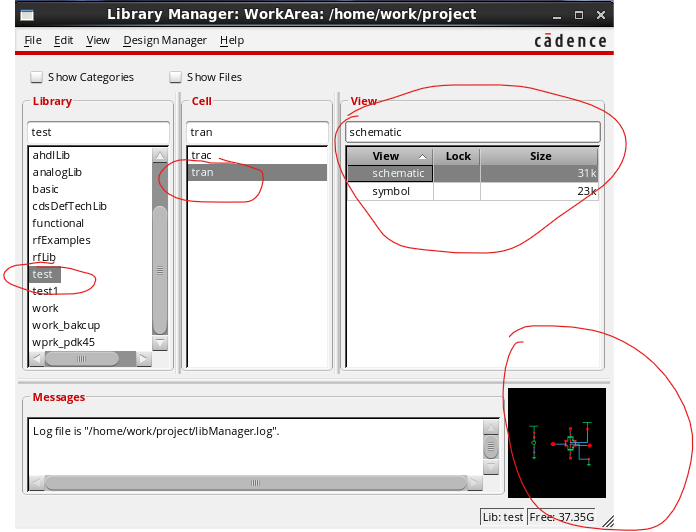

这样,原理图及symbol图就画完了。我们现在就可以库中查看了,在 CIW 窗口(就是输入完命令后显示的那个窗口),点击 Tools — Library Manager,就可以进入到库管理界面。

选择我们建立的 Library(库) test,cell(元件) tran,可以发现,已经有两个View(视图)了,分别是 Schematic(原理图)和 Symbol(符号图),原理中左边有个锁?的标志,这表示我们的原理图还在编辑,没有关闭。

当我们把原理图关闭后,锁?的标志就消失了。

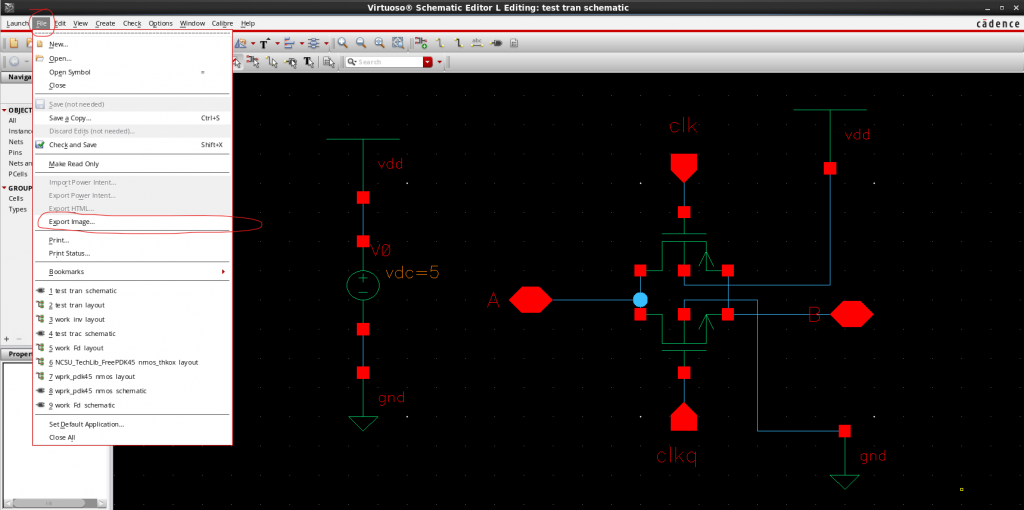

如果你打开文件查看,会发现所有的库,元件,视图其实都对应一个文件夹,在视图(如schematic)文件下才是具体的数据。 如果我们直接将原理图截屏放到 ppt 上展示的话,效果不是太好,这时我们可以导出背景为白色的原理图,如本文的特色图片那样。选择 File — Export image

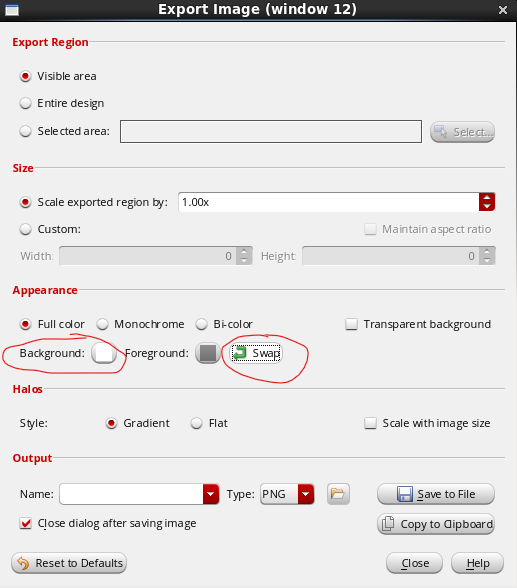

点击 Swap ,将 Background 改为白色, 当然也可以点击 Background 后面的白色那块,将背景改为其它颜色,Foreground 是前景色。

如果在这个过程中遇到了其它问题,欢迎在评论区留言,或者Google一下,也欢迎把具体的解决方法留在评论区,以供后来者参考

欢迎转载,不需注明出处,就说是你写的