功耗管理

本文上次更新于 350 天前,其内容可能已经过时,如果文章内容或图片资源失效,请留言反馈,我会及时处理,谢谢!

对此部分不算熟悉,不一定能够解答疑问(2024.4.19)

总览

- 功耗管理状态有D状态(D states)和L状态(L states)或者其它协议规定的状态(如,S状态)

- 电源管理状态

- D状态

- D状态跟特定的功能相关

- D0是正常工作时的状态,耗电量最大

- D1和D2是位于中间的省功耗状态

- D3Hot是非常低的功耗状态

- D3Cold是电源关闭状态

- D状态

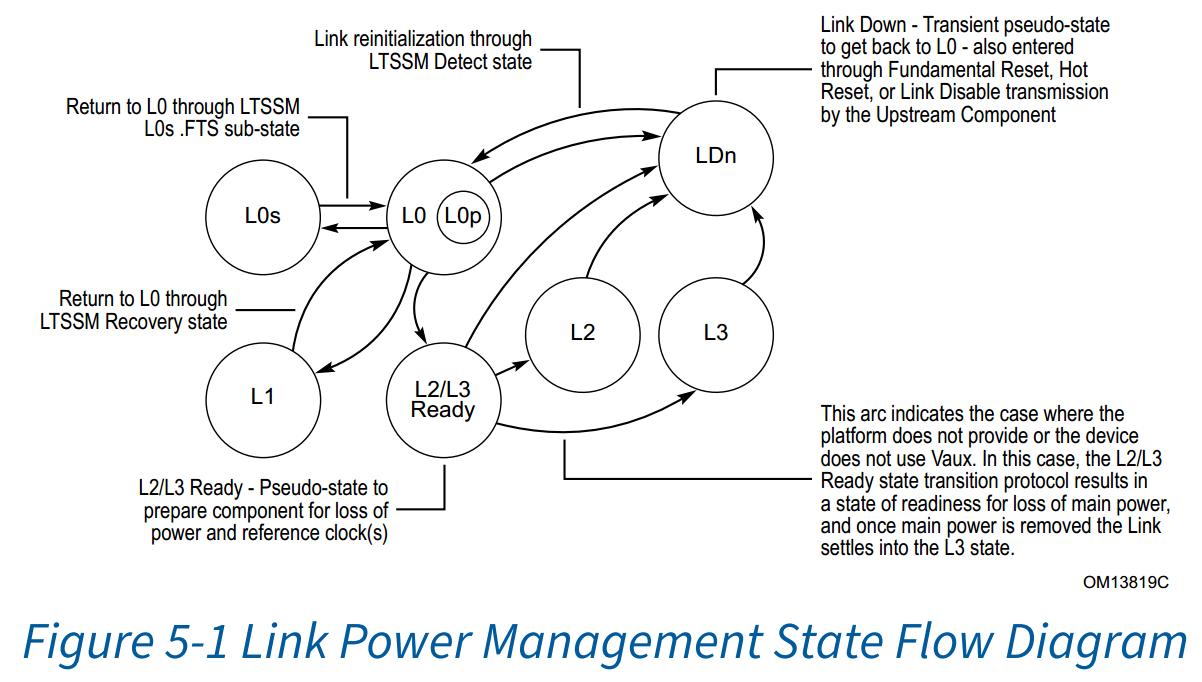

- L状态

- L状态跟特定的链路相关

- L0是正常工作时的状态

- L0p时L0的子状态,相较于L0可以节省部分功耗

- L0s,L1,L1.0,L1.1和L1.2时不同的低功耗状态

- Lx(x=0,1,1,3),x越大,节省功耗越明显

- 电源管理状态提供如下服务

- 识别给定功能(Function)的电源管理能力

- 能够将一个功能转换到特定的电源管理状态

- 通知功能当前的电源管理状态

- 使用特殊的事件唤醒系统(可选)

- 系统唤醒

- 组件(Components)使用电源管理事件(power management event,PME)消息机制来唤醒系统

- 当主电源关闭时,PCIE系统可以提供可选的备用电源(auxiliary power supply,Vaux)来将设备从特殊状态唤醒

- PCIE-PM PME机制将下面两种PME任务分开了:

- 重新激活(唤醒)特定资源(如:重新建立PCIE组件的参考时钟和主电源)

- 向根复合体(Root Complex,RC)发送PME消息,以提供唤醒事件的源

- ASPM

- 活动状态电源管理(Active State Power Management,ASPM)是基于硬件自动完成.当连接上的组件在D0状态时,活动状态机制能够自动节省功耗.

- 链路经过一段事件的空闲后,ASPM物理层协议将idle放在链路上来节省功耗

- 一旦进入低功耗状态,由链路两侧的流量触发过渡到完全运行的L0状态. TODO(翻译问题)

- 软件可以禁止ASPM

链路状态电源管理

- PCIE-PM定义下面的链路电源管理状态

- L0(包括L0p子状态) – 活动状态

- ASPM和PCI-PM兼容电源管理都必须支持L0.

- 所有PCI Express事务和其他操作都是启用.

- L0s – 低恢复延迟,节能“待机”状态.

- 对于ASPM,L0s是可选的状态.除非链路的适用外形规格明确要求L0s支持. TODO(翻译问题)

- 在LTSSM处于L0s期间,所有的主电源,组件的参考时钟和组件内部的PLLs必须一直都是激活状态.

- 如果LTSSM处于Tx_L0s,这个端口禁止发送TLP和DLLP.

- 物理层提供了快速切换到L0状态的机制(通过FTS).

- 当链路双反使用相同(分布式)参考时钟时,从L0s转变到L0的时间期望小于100个符号时间

- 允许组件的发射端处于L0s状态,另外一个组件的发送端处于L0状态.

- L1 – 更高的延迟,低功耗“待机”状态.

- PCI-PM兼容电源管理必须支持L1.对ASPM来说,对L1的支持是可选的,除非是特定的原因. TODO(翻译问题)

- 通过设置L1 PM Substates Control 1寄存器的一个或者更多enabel位可以使能L1子状态,该子状态成为L1.0子状态

- 在L1状态期间,所有的主电源必须处于激活状态.

- 只要它们遵守所宣传的L1退出延迟,就明确允许实施通过应用技术来降低功耗,例如但不限于定期而不是连续检查电气空闲退出,仅在一个通道上检查电气空闲退出并关闭不需要的电路. TODO(翻译问题)

- 在L1状态期间,平台提供的所有组件参考时钟必须使能,除非时钟电源管理(使用CLKREQ#)或者L1 PM子状态允许他们关闭

- 在L1状态期间,组件内部的PLLs可以关闭,在增加了退出延时的情况下可以节省很大的功耗

- 当给定链路上的下游组件的所有功能被编程为D状态而不是D0时,就进入L1状态

- 如果下游组件请求L1 entry(ASPM)并收到请求的肯定确认,也会进入L1状态.

- L1的退出是上游发起的(Upstream-initiated)事务,该事务的目标是下游组件,或者由下游组件发起的事务,该事务是向上游发起. TODO(翻译问题)

- 从L1转换到L0需要几为微秒

- 在L1期间,链路上不允许传输TLP和DLLP

- L1 PM子状态

- 对于PCI—PM和ASPM来讲,低功耗状态L1的子状态L1.1和L1.2是可选的

- 在L1.1子状态,链路上的共模电压必须维持.

- 当链路在L1.0子状态并且进入L1.1子状态的条件满足时,就会进入到L1.1子状态

- 在L1.2子状态,链路上的共模电压不要求保持

- 当链路在L1.0子状态并且进入L1.2子状态的条件满足时,就会进入到L1.2子状态

- 当CLKREQ#信号被使能时,将会退出L1 PM子状态

- L2/L3 Ready – L2/L3状态的中转点

- 需要L2/L3 Ready转换协议支持.

- L2/L3 Ready是一个虚状态(与LTSSM的L2状态相对应)

- 当下游组件或者两端的组件准备移除电源和时钟时,链路就会进入该状态.

- 在PM软件操作设备进入D3状态后,才准备移除电源和时钟,随后呼叫电源管理软件初始化移除电源和时钟的操作.

- 在进入L2/L3 Ready状态后,组件已经准备号移除电源

- 在主电源移除后,如果有备用电源(Vaux)则链路进入L2,如果没有备用电源或者备用电源没有使用则进入L3.

- 对链路而言,L2/L3 Ready时PM虚状态,LTSSM通常是工作在主电源,因此当主电源移除后,链路会关闭

- 在确认PME_Turn_Off消息(如:注入PME_TO_Ack TLP)后,L2/L3 Ready状态进入转换过程必须尽快开始

- 下游组件通过发送PM_Enter_L23 DLLP来进入L2/L3 Ready

- 在L2/L3 Ready状态禁止发送TLP和DLLP

- 从L2/L3 Ready状态返回到L0会经过一些中间状态

- L2 – 使用辅助电源,深度节能状态

- 对L2的支持是可选的,并且取决于是否有辅助电源

- 如果支持该状态,则组件在该状态只使用辅助电源

- 在L2,组件的主电源输入和参考时钟输入是关闭的

- 在L2,链路的任何重新唤醒逻辑(Beacon或者WAKE#),PME文本,或者其它任何”保活”的逻辑都使用辅助电源供电

- 链路在L2不允许传输TLP和DLLP

- L3 – 链路关闭状态

- 当无电源存在时,链路进入L3状态

- LDn – 链路状态过渡到L0时的虚状态

- 该虚装态可以是LTSSM的Detect,Polling,Configuration,Disable,Loopback或Hot Reset.

- L0(包括L0p子状态) – 活动状态

- L状态可能发生的转变

- 协商进入L1和L2/L3 Ready发生在L0状态.只有在协商完成后才能进入L1或者L2/L3 Ready.

- 除非是LDn发生,否则链路功耗管理仍然在L0直到协商完成

- 这些状态和状态跳转与物理层LTSSM的行为不是直接对应的

- 上图中的L0包含LTSSM的L0,Recovery以及Configuration(在链路训练期间)

- LTSSM通常是由主电源供电(不是辅助电源),因为LTSSM在L2或者L3状态时也不会供电

- 下面的示例序列说明了导致进入系统睡眠状态的多步骤链路状态转换过程:

- 系统软件指导下游组件的所有功能到D3Hot.

- 然后,下游组件根据需要启动链路到L1的转换.

- 然后,系统软件使根复体(RC)广播PME_Turn_Off消息,为移除主电源做准备.

- 该消息导致链路对象转换回L0,以便发送该消息,并使下游组件能够使用PME_TO_Ack进行响应.

- 在发送完PME_TO_Ack后,下游组件启动L2/L3 Ready转换协议.

- 整个过程L状态跳转为L0->L1->L0->L2/L3 Ready

- 也可以在不首先将所有功能放入D3Hot的情况下移除电源:

- 系统软件使根复体(RC)广播PME_Turn_Off消息,为移除主电源做准备.

- 下游组件相应PME_TO_Ack.

- 在发送完PME_TO_Ack后,下游组件启动L2/L3 Ready转换协议.

- 整个过程L状态跳转为L0->L2/L3 Ready

- 状态机复位为空闲状态

- 对下游组件而言,在状态机离开空闲状态后的第一个行为是根据协商的类型发送合适条目的DLLPs.

- 如果协商被打断(如:进入到Recovery状态),两端组件的状态机都复位到空闲状态.

- 上游组件必须总是进入到空闲状态,并等待接受能够进入其它L状态的DLLPs

- 下游组件必须始终进入空闲状态,并且必须始终继续发送条目DLLP以重新启动协商.

- 下标总结了每个L状态和平台和组件的行为,”yes”表示需要支持(除非是明确说明),”On”和”Off”表示所需的时钟和电源.”On/Off”表示设计可选

| L状态描述 | S/W使用直接PM TODO(翻译问题) | ASPM使用的 | 平台参考时钟 | 平台主电源 | 组件内部的PLL | 平台辅助电源 | |

|---|---|---|---|---|---|---|---|

| L0/L0p | 完全激活链路 | YES(D0) | YES(D0) | On | On | On | On/Off |

| L0s | 待机状况 | No | Yes1(opt.,D0) | On | On | On | On/Off |

| L1 | 低功耗待机 | Yes(D1-D3Hot) | Yes(opt.,D0) | On/Off6 | On | On/Off2 | On/Off |

| L2/L3 Ready(虚状态) | 移除电源的中间点 | Yes3 | No | On/Off6 | On | On/Off2 | On/Off |

| L2 | 低功耗睡眠状态(所有时钟,主电源关闭) | Yes4 | No | Off | Off | Off | On5 |

| L3 | 关闭(无电源) | n/a | n/a | Off | Off | Off | Off |

| LDn(虚状态) | 过渡到L0之前的虚状态 | Yes | N/A | On | On | On/Off | On/Off |

- 表中的一些注意事项

- 1.对于连接到给定链路两端的组件,在具有独立参考时钟输入的链路配置中,L0s退出延迟将是最大的(与通用的分布式参考时钟相比).

- 2.对于在此状态期间内部关闭其锁相环的组件来说,L1退出延迟最大.

- 3.L2/L3 Ready启动序列在PME_Turn_Off/PME_TO_Ack协议握手完成时启动.它并不属于D状态的过渡或者ASPM的过渡 TODO(翻译问题)

- 4.却决于平台的具体实现,系统的休眠状态可以使用L2状态,过渡到完全关闭(L3)或者让链路处于L2/L3 Ready状态.L2/L3 Ready状态转换协议由下游组件在接收到PME_Turn_Off TLP消息并得到TLP确认后发起.虽然平台对L2睡眠状态配置的支持是可选的(取决于辅助电源的可用性),但是要求组件协议支持将链路转换为L2/L3 Ready状态.

- 5.L2和L3之间的不同时是否存在辅助电源.在完成L2/L3Ready状态转换协议之后并在主电源被移除之前,链路已经表示它准备好移除主电源.

- 6.低功耗移动或手持设备可以通过“时钟请求”(CLKREQ#)机制通过时钟门控参考时钟来降低功耗.

PCI-PC软件兼容机制

功能的设备电源管理状态(D-状态)

- D0状态为链路工作时的状态

- 其他状态是各种级别的降低功率,其中函数不运行或支持有限的一组操作. TODO(翻译问题)

- D1和D2是中间状态,旨在为系统设计人员提供更大的灵活性,以平衡给定器件类别的节能、恢复时间和低功耗特性可用性.

- 例如,D1状态可以被支持为比D2稍高的功耗状态,但是它产生的恢复时间比D2更快

- D3电源管理状态是一种特殊的电源管理状态,可以通过软件或物理移除其电源将函数转换为D3.

- 从这个意义上讲,两个D3变体被指定为D3Hot和D3Cold,其中下标分别表示主电源的存在或不存在.

- D3Hot中的函数允许软件通过写入函数的PMCSR寄存器转换到D0状态.

- 处于D3Cold状态的功能可以通过重新应用主电源并使用基本复位(Fundamental Reset)来转换到D3uninitialized状态.

- 所有函数必须支持D0和D3状态(D3Hot和D3Cold).D1和D2状态可选.

D0状态

- 所有函数都必须支持D0状态

- D0分为两个不同的子状态,”未初始化(un-initiated)”子状态和”活跃(active)”子状态

- 当组件退出常规复位(Conventional Reset)时,该组件的所有函数都进入D0uninitialized状态

- 当函数完成功能复位(Function Level Reset,FLR)后,它会进入D0uninitialized

- 配置完成后函数进入D0active状态,即PCI Express函数处于完全可操作状态.

- 当一个函数的内存空间使能,I/O空间使能或总线主时,或使能位已设置(即使后面被清掉,函数仍然处于D0active状态),该函数就会进入active状态

D1状态

- D1状态是可选的

- 当处于D1状态时,除了消息(Message)之外,函数不能在链路上发起任何请求TLPs

- 配置(Configuration)请求和消息请求是函数在D1状态下唯一接受的TLP

- 所有其他收到的请求必须作为不支持的请求处理,并且所有收到的完成(Completions)可以选择性地作为不支持的完成处理.

- 如果收到的TLP导致错误(例如

- 在D1中检测到不支持的请求(Unsupported Request),并且启用了报告功能,如果链路不在L0中,则必须返回到L0,并且必须发送错误消息

- 如果错误是由收到的TLP以外的事件引起的(例如,完成超时)并在D1时被检测到,当函数被编程回D0状态时必须发送一个错误消息.

- 注意,函数的软件驱动程序参与了函数从D0到D1的转换过程.

- 它通过保存任何功能状态(如有必要)以及以其他方式准备功能以转换到D1来促进该过程.

- 作为此静态过程的一部分,函数的软件驱动程序必须确保任何中间事务TLP(即未完成的请求)在将控制权交给系统配置软件之前被终止,然后系统配置软件将完成向D1的过渡.

D2状态

- D2支持是可选的.

- 当一个函数目前没有被使用,并且可能在一段时间内不会被使用时,它可能会进入D2中.

- 这种状态要求函数提供显著的功耗节省,同时仍然保留完全恢复到先前状态的能力.

- 当处于D2状态时,除了消息之外,函数不能在链路上发起任何请求TLPs

- 配置(Configuration)请求和消息请求是函数在D2状态下唯一接受的TLP

- 所有其他收到的请求必须作为不支持的请求处理,所有收到的完成可以选择作为不支持的完成处理.

- 如果在D2中检测到由收到的TLP引起的错误(例如,不支持的请求),并且启用了报告功能,如果链路尚未在L0中,则必须返回到L0,并且必须发送错误消息.

- 如果在D2中检测到由接收到的TLP以外的事件(例如,完成超时)引起的错误,则当函数被编程回D0状态时,必须发送错误信息.

- 注意,函数的软件驱动程序参与了函数从D0到D2的转换过程.

- 它通过保存任何功能状态(如有必要)以及以其他方式准备功能以转换到 D2 来促进该过程.

- 作为静默过程的一部分,函数的软件驱动程序必须确保在将控制权交给系统配置软件之前,任何事务中的TLP(即未完成的请求)都被终止,然后系统配置软件将完成向D2的过渡

- 系统软件必须将该功能恢复到D0active状态,才能访问内存(Memory)或I/O空间.

- 从一个函数从D2编程到D0到向该函数发出下一个请求之间的最小恢复时间要求为200 μs.

- 未定义在此恢复时间窗口内收到请求的行为

D3状态

- 必须支持D3(D3Cold和D3Hot)状态

- 如果设置PMCSR寄存器中的No_Soft_Reset字段,处于D3Hot状态的函数需要维护函数上下文 TODO(翻译问题). 在这种情况下,系统软件不需要在从D3Hot转换到D0后重新初始化函数,函数将处于active状态).

- 如果No_Soft_Reset字段被清掉,则功能上下文不需要在D3Hot状态下由函数维护,但不能保证功能上下文将被清除,软件也不能依赖于这种行为.因此,在这种情况下,系统软件需要在转换到D0后完全重新初始化该函数,因为该函数将处于D0uninitialized状态.

- 如果链路状态已过渡到L2/L3 Ready状态,则该函数将被重置,无论No_Soft_Reset位的值如何.

- 在访问函数之前,除非PCI-PM电源管理能力寄存器中的Immediate_Readiness_on_Return_to_D0位被设置,否则系统软件必须允许D3Hot->D0转换的最小恢复时间至少为10毫秒. 例如,在可访问之前,D3Hot->D0过渡组件可以使用此恢复时间来引导其任何组件接口(例如,从串行ROM).

- 尝试在恢复时间内定位该功能(包括配置请求数据包)将导致未定义的行为.

D3Hot状态

- 配置和消息请求是处于D3Hot状态下,功能所接受的唯一TLP

- 所有其它接收到的请求必须作为不受支持的请求处理,所有接收到的完成也可以选择性的作为不支持的完成处理.

- 如果在D3Hot中检测到由收到的TLP引起的错误(例如:不支持的请求),并且启用了报告功能,如果链路尚未在L0中,则必须返回到L0,并且必须发送错误消息

- 如果在D3Hot中检测到由接收到的TLP以外的事件(例如,完成超时)引起的错误,则可以在函数被编程回D0状态时发送一条错误消息.

- 一旦进入D3Hot,该功能可以稍后过渡到D3Cold(通过从其主机组件中移除电源).

- 注意,函数的软件驱动程序参与了函数从D0到D3Hot的转换过程

- 它通过保存任何功能状态(否则会因移除主电源而丢失)以及准备功能以过渡到D3Hot来帮助该过程. TODO(翻译问题)

- 作为此静态过程的一部分,函数的软件驱动程序必须确保任何未完成的事务(即,具有未完成的请求)在将控制权交给系统配置软件之前终止,然后完成向D3Hot的过渡.

- 请注意,D3Hot也是一种有用的状态,可用于减少正在运行的系统中空闲组件的功耗.

- 在D3Hot中的函数被允许由软件转换(写入它们的PMCSR PowerState字段)到D0active状态或D0uninitialized状态.

- 只要提供电源和时钟,D3Hot中的函数就必须响应配置空间访问,以便软件可以将它们返回到D0.

- 请注意,在从D3Hot转换到D0期间或立即转换之后,不需要该函数生成内部硬件复位(参见PMCSR中No_Soft_Reset位的使用).

- 如果不需要内部复位,在完成D3Hot到D0active状态后,除了写入PowerState字段外,不需要额外的操作系统干预

- 如果需要内部复位,设备会返回到D0uninitialized状态,并需要在设备上进行一次完全的重新初始化.

- 完整的重新初始化序列将设备返回到D0active

- 如果设备支持PME事件,并且设置了PME_En,则需要在D3Hot中保留PME上下文.

- 在用PowerState命令转换回D0时,还必须保留PME上下文.

D3Cold状态

- 函数主电源断电后,会切换到D3Cold状态

- 通电序列及其相关的冷复位将函数从D3Cold状态转换为D0uninitialize状态,并且开机默认值将由硬件恢复到功能,就像初始开机时一样.此时,软件必须执行函数的完全初始化,以重新建立所有功能上下文,完成函数恢复到其D0active状态.

- 当设置了PME_En后,支持D3Cold唤醒功能的函数必须在PMCSR中维护它们的PME上下文,以便PME服务例行软件在恢复过程中进行检查.附加上下文的保留是特定于实现的.

- 当系统软件对其PCI-PM兼容PMCSR的断言功能的PME_Status位执行“写1清除”配置事务时,功能的 PME 断言得到确认.

- 必须使用辅助电源来支持函数中的PME事件检测,链接重新激活以及保存D3Cold中的PME上下文.

- 请注意,一旦由于链路重新激活,I/O层次结构恢复到完全通信状态,那么唤醒代理就会将PME消息传播到层次结构的根,指示PME事件的来源.

PM软件控制链路电源管理状态

- 链路的电源管理状态由下游组件的D状态决定

| 下游组件D状态 | 允许的上游组件D状态 | 允许的互连状态 |

|---|---|---|

| D0 | D0 | L0,L0s,L1(1),L2/L3 Ready |

| D1 | D0-D1 | L1,L2/L3 Ready |

| D2 | D0-D2 | L1,L2/L3 Ready |

| D3Hot | D0-D3Hot | L1,L2/L3 Ready |

| D3Cold | D0-D3Cold | L2(2),L3 |

- 注意

- (1)对ASPM L0s和ASPM L1支持的需求是特定于外形因素的。

- (2)如果辅助电源是由平台提供的,则链路在L2中休眠。没有辅助电源时,L态是L3。

- 与PCI-PM兼容的电源管理相关的规则如下:

- 设备处于D0,D1,D2和D3Hot时,在收到PME_Turn_Off消息后,必须发送PME_TO_Ack消息作为响应。

- 任何设备在D状态下,在执行PME_Turn_Off/PME_TO_Ack握手序列之后,下游组件必须使用PM_Enter_L23 DLLP请求链路转换到L2/L3 Ready

- 根据L2/L3 Ready入口转换协议,下游组件必须为主电源和参考时钟的丢失做好准备。

- 单功能设备的上行端口仅在功能被编程到D1、D2或D3Hot的情况下,就必须发起到L1的链路状态转换

- 对于交换机(Switch),系统软件负责确保交换机上行端口的任何 D 状态编程都以符合层次结构范围 PM 策略的方式完成(即,上行端口不能编程为比最活跃的下游端口和下游连接的组件/功能更不活跃的D状态) TODO(翻译问题)

- 非ARI多功能设备的上游端口不得启动到L1(代表 PCI-PM)的链路状态转换,直到其所有功能都被编程为非D0的D状态。

- ARI设备的上游端口必须至少有一个功能被编程为非D0状态,并且它的所有功能都处于非D0状态或D0uninitialized状态,然后上游端口才能启动到L1的链路状态转换(代表PCI-PM)。

- 对于SR-IOV设备,链路功率状态完全由PFs中的设置控制,而不用考虑VFs的D状态。VF功率状态不影响链路的功率状态。

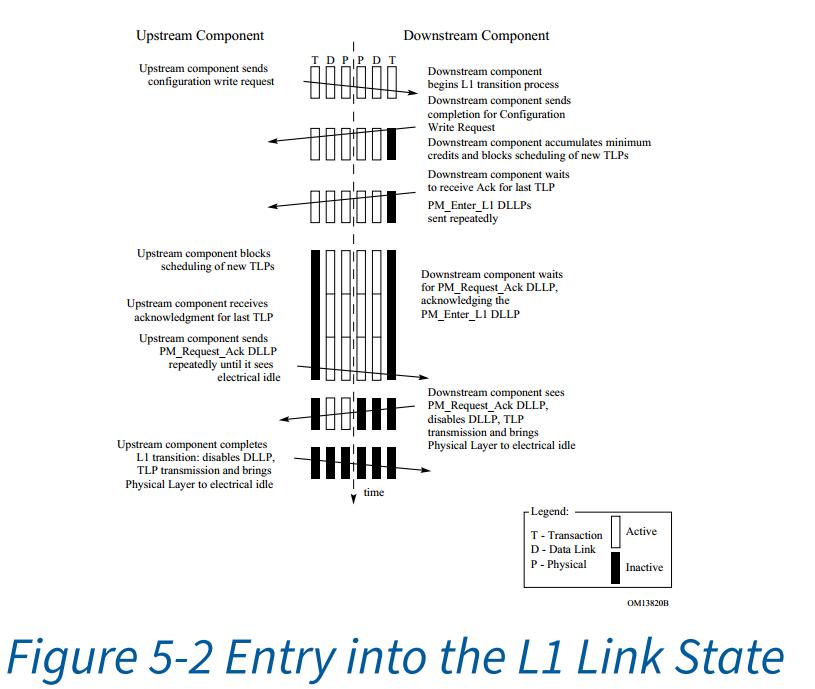

进入L1状态

- 下图描述了电源管理软件将下游连接的组件编程为低功耗状态(可以是D1,D2或者D3Hot状态)的直接结果,即链路转换为L1状态的过程。此图和随后的描述概述了正在被编程为非D0状态的单个功能下游组件的转换过程

- 下面的文本提供了所示的链路状态转换过程的附加详细信息,PM软件要求:

- PM软件向下游功能的PMCSR发送一个配置写请求TLP,以改变下游功能的D状态(例如从D0到D1)。

- 下游组件链路状态转换启动过程:

2. 下游组件将与配置写入请求相对应的完成调度到其PMCSR PowerState字段并考虑所需的完成信用 TODO(翻译问题)

3. 然后,下游组件必须等待,直到它至少积累了为所有启用的VC发送任何FC类型的最大可能数据包所需的最小信用数(如果它还没有这样的信用). 然后暂停所有事务层TLP调度。

4. 然后下游组件等待,直到它收到PMCSR写入完成的响应,以及它之前发送的任何其他TLP。 TODO(翻译问题).如果数据链路层规则(在非切换模式下运行时)或切换Ack/Nak规则(在切换模式下运行时)要求这样做,组件必须从其适当的重试缓冲区中重传TLP。

5. 一旦所有下游组件的TLP被确认,下游组件开始传输PM_Enter_L1 DLLP.下游组件重复发送该DLLP,在Non-Flit模式下,PM_Enter_L1 DLLP的后续传输之间的空闲符号时间不超过8(当使用8b/10b编码时)或32(当使用128b/130b编码时)。PM_Enter_L1传输之间的其他DLLPs和SKP有序集的传输在任何时候都是允许的,并且不影响这个空闲时间限制。下游组件继续像上面描述的那样传输PM_Enter_L1 DLLP,直到它收到来自上游组件的响应(PM_Request_Ack).下游组件必须继续接受来自上游组件的TLP和DLLP,并根据需要继续响应DLLP,包括FC更新DLLP和Ack/Nak DLLP。任何被阻止传输的TLP(包括对收到的TLP的响应)必须被存储以供以后传输,并且必须使下游组件在L1进入后尽快启动L1退出 - 上游组件链路状态转换过程:

6. 上游组件收到PM_Enter_L1 DLLP后,会阻断所有TLP的调度。

7. 然后,上游组件必须等待,直到它收到了确认(acknowledgement),该确认是针对最后一个发送的TLP。如果数据链路层规则(在非Flit模式下操作)或Flit Ack/Nak规则(在Flit模式下操作)要求这样做,上游组件必须从其适当的重传缓冲区重传TLP。

8. 一旦上游组件(下游端口)的所有TLP都得到确认,上游组件必须向下游发送PM_Request_Ack DLLP,而不管是否有未完成的请求。Non-Flit模式下,在PM_Request_Ack DLLP的后续传输之间,上游组件重复发送此DLLP,不超过8个(当使用8b/10b编码时)或32个(当使用128b/ 130b编码时)个空闲符号时间.在PM_Request_Ack传输之间的任何时间都允许传输SKP有序集,并且不会导致此空闲时间限制(TODO(翻译)).上游组件继续发送如上所述的PM_Request_Ack DLLP,直到它观察到它的接收通道进入电气空闲状态。 - 完成L1链路状态转换:

9. 一旦下游组件在其接收通道上捕获了PM_Request_Ack DLLP(表示上游组件承认向L1请求的转换),然后就禁用DLLP传输,直接使上游物理链路进入电气空闲状态。

10. 当上行组件接收的Lanes状态变为电气空闲时,上行组件停止发送PM_Request_Ack DLLP,并关闭DLLP的发送,使自己的发射Lanes状态变为电气空闲,完成链路到L1的转换。 - 由于下游组件被编程为非DO状态,当两个组件的互连链路处于L1时,两个组件暂停其流量控制更新的操作,如果实现,更新FCP定时器计数器机制。

- L1中链路两端的组件可以选择性地禁用其内部锁相环,以节省更多的功耗.但是,平台提供的主电源和参考时钟必须继续提供给L1链路两端处于L1的L1.0子状态的组件。

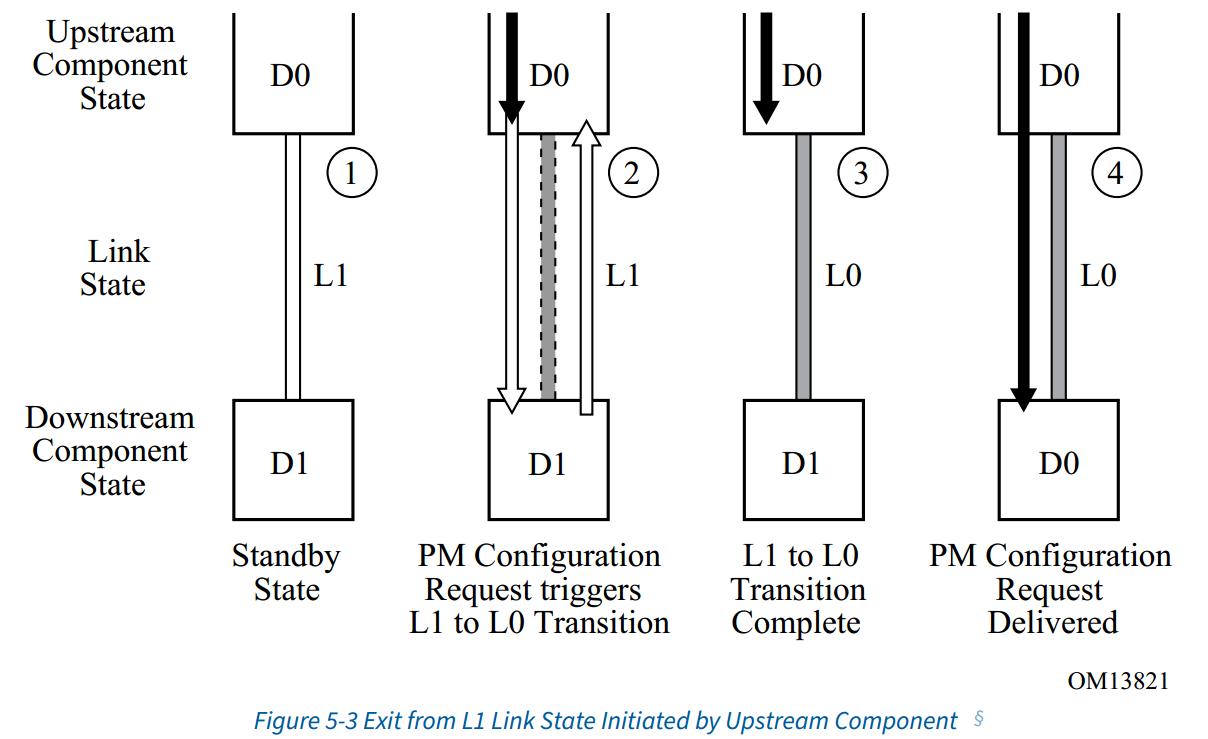

从L1状态退出

- L1退出可以由链路两端的组件发起。

- 从L1退出后,建议下游组件在L1退出后1μs内为所有已启用的VCs和FC类型发送流控更新DLLP。

- 如果某个组件需要在链路上发送TLP,则必须由该组件发起L1退出的请求

- 上游组件必须在下游端口发起L1退出,即使它没有传输TLP所需的流量控制信用

- 在L1退出之后,上游组件必须等待从下游组件接收所需的信用。

- 从L1退出到L0的例子

- 电源管理软件发起一个周期的配置操作,目标是一个PM配置寄存器(在这个例子中是PMCSR的PowerState字段),这个寄存器位于下游组件的一个函数中(例如,将函数恢复到D0状态)。

- 上游组件检测到一个配置周期是针对当前处于低功耗状态的链路,因此发起该链路到L0状态的转换。

- 如果链路处于L1的L1.1或L1.2子状态,则上游组件启动链路到L1的L1.0子状态的转换。

- 链路的两个方向都进入链路训练,导致链路过渡到L0状态。

- 当链路的两个方向都恢复到L0状态后,上游端口将配置报文发送到下游端口

进入到L2/L3 Ready状态

- 转换到L2/L3就绪状态的过程与L1进入状态的过程类似。两者之间有一些细微的区别,如下所述:

- L2/L3 Ready入口转换协议不会立即导致链路进入L2或L3状态。

- 过渡到L2/L3 Ready是有效的握手,以建立下游组件为断电做好准备。

- 当平台去除组件的电源和参考时钟时,最终实现L2或L3。

- L2/L3 Ready入口转换的时间由PME_Turn_Off/PME_TO_Ack握手序列的完成来指示

- 在开始向L2/L3就绪过渡之前,下游部件的任何动作都必须为其失去电源做好准备。

- 一旦所有断电和时钟丢失的准备工作完成,下游组件通过向上游发送PM_Enter_L23 DLLP发起L2/L3 Ready entry。

- L2/L3 Ready入口转换协议使用PM_Enter_L23 DLLP。

- PM_Enter_L23 DLLP会持续发送,直到收到确认或断电。

功耗管理时间机制

动机

- PCI Express PME机制与[PCI] PME机制是软件兼容的。

- 电源管理事件由功能生成,作为请求PM状态更改的一种方式。

- 电源管理事件通常用于使系统或单个功能从低电源状态恢复。

- 电源管理软件可以将一个层次转换为低功耗状态,并将这些设备的上游链路转换为非通信L2状态.因此,PCI Express PME生成机制分为两个部分:

- 唤醒非通信层次结构(wakeup)。只有当发起PME的设备的上游链路处于非通信L2状态时,才需要执行此步骤,因为在这种状态下,设备不能向上游发送PM_PME消息。

- 发送一个PM_PME消息到层次结构的根节点

- 源自PCI Express Endpoints或PCI Express Legacy Endpoints的PME指示以TLP消息的形式传播到根复体。

- PM_PME消息标识层次结构中的请求代理(通过PM_PME消息头的请求者ID)。

- PM_PME消息中的显式标识旨在促进更快的PME服务例程响应,从而缩短恢复时间。

- 如果RCiEP与根复杂事件收集器相关联,则该根复杂事件收集器必须报告源自该RCiEP的任何PME指示。

- 来自根端口本身的PME指示通过相同的根端口报告。

链路唤醒

- 链路唤醒机制提供了一种向平台发送信号的方法,以重新建立其域内组件的电源和参考时钟。

- 定义了两种唤醒机制:Beacon和WAKE#

- Beacon机制使用带内信令实现唤醒功能

- 对于支持唤醒功能的组件,实现所针对的外形规格决定了唤醒机制的支持要求。

- 针对某些交换机端口使用Beacon而其他端口使用WAKE#的应用程序的交换机组件必须适当地转换唤醒机制

- 在使用WAKE#作为唯一唤醒机制的应用程序中,根复核不需要支持接收Beacon。

- wake#机制使用边带信令来实现唤醒功能。

- wake#是由请求唤醒的组件断言并由相关电源控制器观察到的“打开漏极”信号。

- WAKE#仅针对某些形状因子定义,相关的形状因子规范中包含了WAKE#的详细规范。

- 特定的外形规格可能需要使用Beacon或wake#作为唤醒机制。

- 当WAKE#被用作唤醒机制时,一旦WAKE#被断言,断言函数必须继续驱动信号低电平,直到主组件电源恢复,正如基本复位不活动所指示的那样。

- 系统不需要以这样一种方式路由或缓冲wake#,即端点保证能够检测到信号已被另一个函数断言。

- 在使用任何唤醒机制之前,必须通过软件在PMCSR中设置函数的PME_En位来启用函数。PME_Status为是黏贴位,如果辅助电源可用并且它们被启用用于唤醒事件((此要求也适用于PMCSR中的PME_En位和设备控制寄存器中的Aux Power PM Enable位),函数必须通过复位来维持PME_Status位的值,

- 允许从D3Cold状态产生PME的系统必须在主系统电源断开时提供辅助电源以支持链路唤醒.如果软件允许,组件只能消耗辅助电源.

- 在所有参与链路唤醒的组件中,包括所有必须传播Beacon信号的组件,都需要软件来启用辅助功耗.在传统(legacy)系统软件存在的情况下,这是系统固件的责任。

- 无论使用何种唤醒机制,一旦重新激活并训练了链接,请求代理就会向根复合体(RC)上游传播一条PM_PME消息

- 从电源管理的角度来看,这两种唤醒机制提供相同的功能

PME同步

- PCI Express-PM引入了一个栅栏机制,用于启动电源移除序列,同时还协调平台电源管理控制器的行为和PCI Express代理的PME处理。

- 在主组件电源和参考时钟关闭之前,根综合体或交换机下游端口必须发出广播消息,指示层次结构中该点的所有下游代理停止发起任何后续PM_PME消息,在收到PME_Turn_Off消息后立即生效。

- 每个PCI Express代理都需要响应TLP“确认”消息PME_TO_Ack,该消息总是路由到上游.

- 在所有情况下,PME_TO_Ack消息必须终止于PME_Turn_Off消息的起始点

如果在这个过程中遇到了其它问题,欢迎在评论区留言,如果你已解决,也欢迎把具体的解决方法留在评论区,以供后来者参考

图挂了

@cszdzc 感谢提醒,已更新图片