PCIe – LTSSM Polling

1. Polling 状态

- 目的 : 实现 bit lock (位锁定),Symbol lock (符合锁定) 和 Lane polarity (lane 极性反转)

- 存在的子状态 :

Polling.Active,Polling.Compliance和Polling.Configuration - 状态跳转图片和文字如有冲突,以图片为准,图片更新更加频繁

2. Polling.Active

2.1 Polling.Active时的行为

- 发射机在Detect状态检测到Receiver的所有lane上发射TS1 Ordered Set, 并且TS1中的Lane number(Symbol 1)和Link number(Symbol 0)都设为 PAD

- 在此状态,必须设置好 TS1 中的 Symbol 4 (速度指示标识)为port支持的所有速度(这个速度是在2.5GT/s-32.0GT/s,如果支持64.0GT/s,不允许在此状态声明),包括不准备用的

- port不允许在此状态声明高于32.0GT/s速度

- 在从 ei 退出后,发射机必须等到 TX 共模模式稳定后,才可以发送 TS1 Ordered Sets

- 进入该状态 192ns 之内,发射机必须用 Transmit Margin field ( Link Control 2 寄存器的 bit[9:7] )中的默认电压发射 patterns, 直到进入 Polling.Compliance 或者 Recovery.Rcvrlock 状态

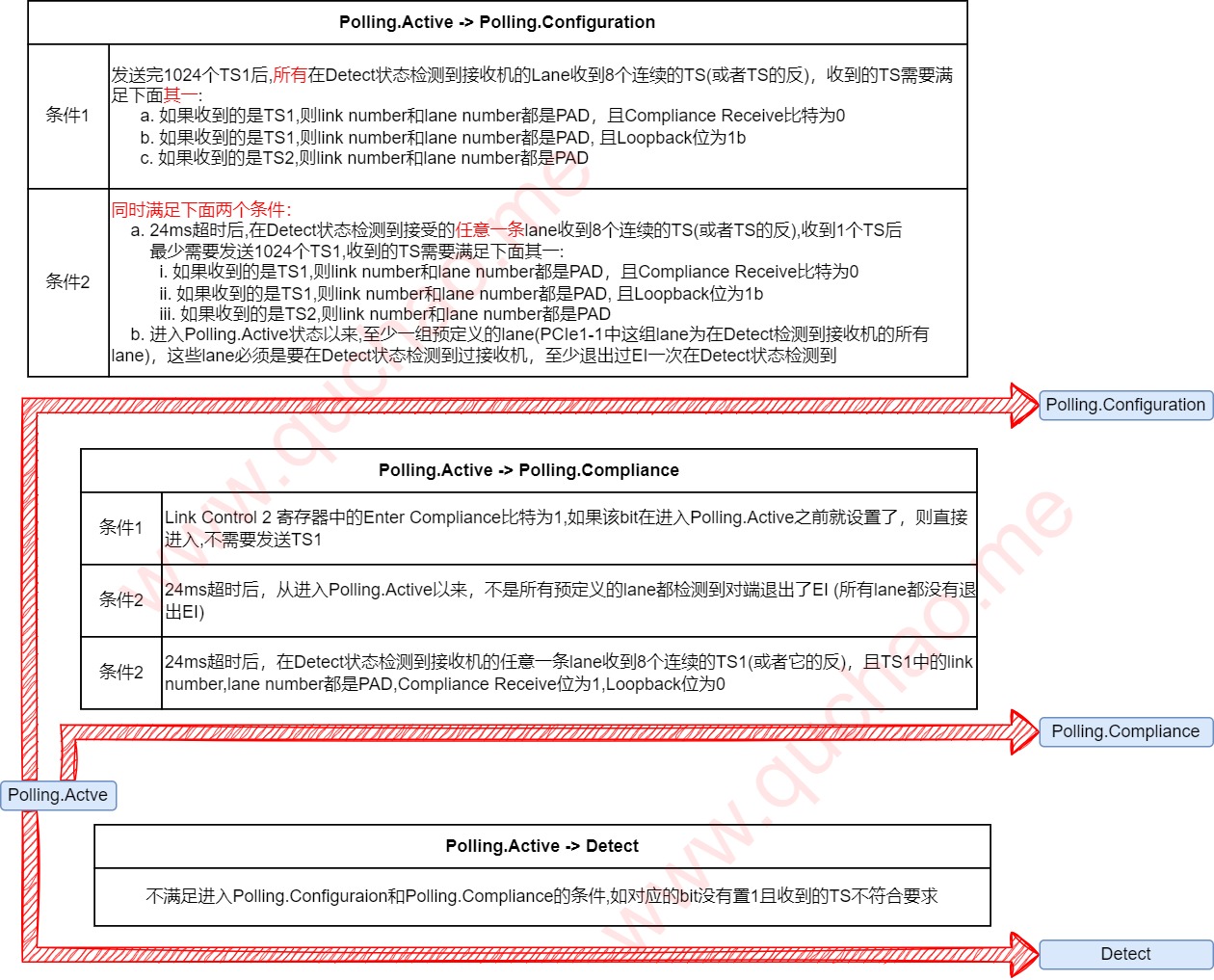

2.2 Polling.Active状态跳转

- Polling.Active可以实现的跳转

- Polling.Active -> Polling.Configuration

- Polling.Active -> Polling.Compliance

- Polling.Active -> Detet

2.2.1 Polling.Active -> Polling.Configuration

| 条件 | 跳转原因 |

|---|---|

| 条件1 | 发送完1024个TS1后,所有在Detect状态检测到接收机的Lane收到8个连续的TS(或者TS的反,如本应该收到4a,但实际收到的是b5) 收到的TS需要满足下面其一: a. 如果收到的是TS1,则link number和lane number都是PAD,且Compliance Receive比特为0 b. 如果收到的是TS1,则link number和lane number都是PAD, 且Loopback位为1b c. 如果收到的是TS2,则link number和lane number都是PAD |

| 条件2 | 同时满足下面两个条件: a. 24ms超时后,在Detect状态检测到接受的任意一条lane收到8个连续的TS(或者TS的反),收到1个TS后最少需要发送1024个TS1,收到的TS需要满足下面其一: i. 如果收到的是TS1,则link number和lane number都是PAD,且Compliance Receive比特为0 ii. 如果收到的是TS1,则link number和lane number都是PAD, 且Loopback位为1b iii. 如果收到的是TS2,则link number和lane number都是PAD b. 进入Polling.Active状态以来,至少一组预定义的lane(PCIe1-1中这组lane为在Detect检测到接收机的所有lane),这些lane必须是要在Detect状态检测到过接收机,至少退出过EI一次在Detect状态检测到 note : 能收到 TS 的 lane 一定是退出了 EI 状态。 但是退出了 EI, 不一定能收到 TS, 收到的 TS 也不一定对 |

2.2.2 Polling.Active -> Polling.Compliance

- Q : 条件2中这里协议写的是not all lane, 这里的not all not是指所有lane呢还是任意一条lane?

- A : 这里可能却决于设计的具体实现。但是需要注意

-

- 这里的not all lane 是加了限定 predetermined set of Lanes,也就是在

Detect状态检测到接收机的这些lane。

- 这里的not all lane 是加了限定 predetermined set of Lanes,也就是在

-

- 如果是任意一条lane的话,进入

Polling.Configuration的优先级要大于进入Polling.Compliance,比如在Detect状态检测到了4条lane,有一条退出EI,有三条没有退出EI,然后退出EI的lane收到的符合要求的TS,那也会进入Polling.Configuratioin,如果退出EI的这条lane没有收到符合要求的TS呢,那就得看设计得具体实现,是需要所有lane都没退出EI还是只需要任意一条就行了。

- 如果是任意一条lane的话,进入

-

- A : 这里可能却决于设计的具体实现。但是需要注意

| 条件 | 跳转原因 |

|---|---|

| 条件1 | Link Control 2 寄存器中的Enter Compliance比特为1,如果该bit在进入Polling.Active之前就设置了,则直接进入,不需要发送TS1 |

| 条件2 | 24ms超时后,从进入Polling.Active以来,不是所有预定义的lane都检测到对端退出了EI (所有lane都没有退出EI) |

| 条件3 | 24ms超时后,在Detect状态检测到接收机的任意一条lane收到8个连续的TS1(或者它的反),且TS1中的link number,lane number都是PAD,Compliance Receive位为1,Loopback位为0 |

2.2.3 Polling.Active -> detect

| 条件 | 跳转原因 |

|---|---|

| 条件1 | 不满足进入Polling.Configuraion和Polling.Compliance的条件,如24ms超时后对应的bit没有置1且收到的TS不符合要求 |

3. Polling.Configuration

3.1 Polling.Configuration时的行为

- 接收机必须处理极性反转 (如果有必要的话)

- 进入此状态是,Transmit Margin field (Link Control 2寄存器的 bit[9:7]) 必须为 000b

- 发射机 Polling.Compliance sequence 设置更新 (待续)

- 在 Detect 状态检测到 Receiver 的所有 lane 发送 TS2

- link number和lane number为PAD

- 在此状态就是表明支持的所有速度(这个速度必须是在2.5GT/s-32.0GT/s之间,如果支持64.0GT/s,则不允许声明),即使是不打算用的,即设置 Data Rate Identifier (Symbol 4)

- 在此状态不允许申明支持高于32.0GT/s的速度

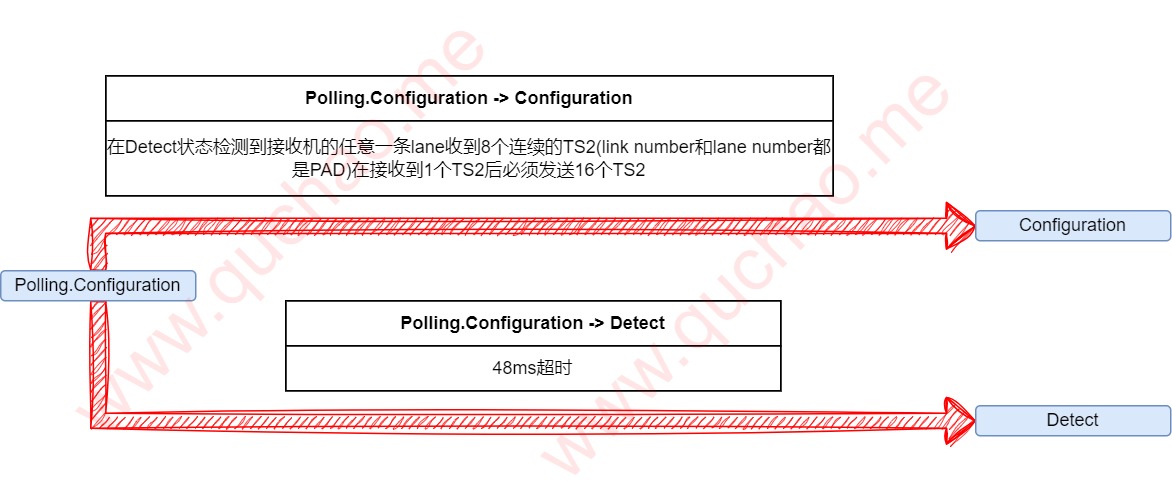

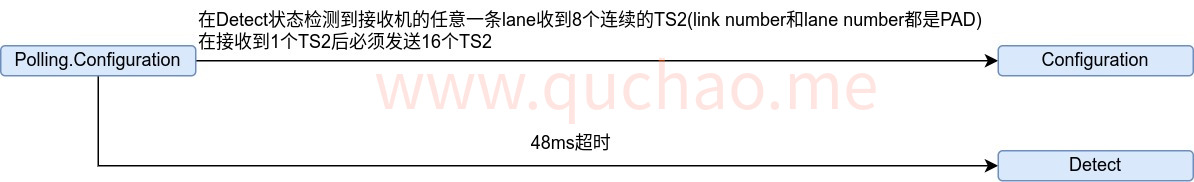

3.2 Polling.Configuration状态跳转

- Polling.Configuration可以实现的跳转

- Polling.Configuration -> Configuration

- Polling.Configuration -> Detect

3.2.1 Polling.Configuration -> Configuration

| 条件 | 跳转原因 |

|---|---|

| 条件1 | 在Detect状态检测到接收机的任意一条lane收到8个连续的TS2(link number和lane number都是PAD)在接收到1个TS2后必须发送16个TS2 |

3.2.2 Polling.Configuration -> Detect

| 条件 | 跳转原因 |

|---|---|

| 条件1 | 48ms 超时 |

4. Polling.Compliance

4.1 Polling.Compliance时的行为

- 进入时会采样 Transmit Margin field (Link Control 2 寄存器的 bit[9:7]); 发射引脚在进入此状态 192ns 之类仍然有效; 并且 ltssm 在此子状态时一直有效

- polling.compliance主要需要确定三件事

- 确定发射机发送pattern的速度

- 确定发射机发送pattern的De-emphasis/preset

- 发送compliance pattern的类型,是compliance pattern还是modified compliance pattern或者jitter compliance pattern等

4.1.1 polling.compliance确定速度和De-emphasis/preset

- 选择发送compliance pattern的速度和de-emphasis/preset,算法如下:

| 原因 | 速度选择 | de-emphasis/preset | |

|---|---|---|---|

| port只支持2.5GT/s | 2.5GT/s | -3.5dB | |

| 收到8个连续的TS1(Compliance Receiver为1,Loopback bit为0) | 本端支持64.0GT/s,在polling.Active收到的TS1OS中Flit Mode Supported为1且supported Link Speeds为10111b(对端支持64.0GT/s) | 64.0GT/s | 收到的EQ TS1OS中的Transmitter Preset比特.如果没有收到EQ TS1OS或者Transmitter Preset是保留的,则发射机根据特定的行为选择一个支持的值 |

| 本端不支持64.0GT/s或者对端不支持64.0GT/s | 由最高通用传输速度和本端发送TS1中的Data Rate Identifiers(symbol 4)决定 | 2.5GT/s和5.0GT/s根据收到的TS1中的Selectable De-emphasis bit(Symbol 4 bit 6)决定。8.0GT/s以及更高,根据收到的EQ TS1OS中的Transmitter Preset比特决定。如果没有收到EQ TS1OS或者Transmitter Preset是保留的,则发射机根据特定的行为选择一个支持的值 | |

| Link Control 2寄存器中的Enter Compliance比特为1 | 根据Link Control 2寄存器中的Target Link Speed字段决定 | 2.5GT/s和5.0GT/s,如果Link Control 2寄存器中的Compliance Preset/De-emphasis字段为0001b,select_deemphasis变为1(表明de-emphasis为-3.5dB)。8.0GT/s及以上,每条lane上select_preset变量设置为Link Control 2寄存器的Compliance Preset/De-emphasis(bit[15:12]),其值必须是有效的编码 | |

| 没有检测到退出EI进入Polling.Compliance(如通过tx端接50欧姆等效负载进入) | 根据进入polling.compliacne的次数来选择速度 | 根据进入polling.compliacne的次数来选择发射机的De-emphasis或者preset值 | |

- 没有检测到退出EI进入polling.compliance,速度和de-emphasis/preset的选择如下

| Setting Nos(进入Polling.compliance的次数) | 速率 | 发射机De-emphasis或preset |

|---|---|---|

| #1 | 2.5GT/s | -3.5dB |

| #2,#3 | 5.0GT/s | -3.5dB(#2),-6.0dB(#3) |

| #4到#14 | 8.0GT/s | preset编码从0000b到1010b,按顺序增加 |

| #15到#25 | 16.0GT/s | preset编码从0000b到1010b,按顺序依次增加 |

| #26到#34 | 16.0GT/s | preset编码为0100b |

| #35到#45 | 32.0GT/s | preset编码从0000b到1010b,按顺序依次增加 |

| #46到#54 | 32.0GT/s | preset编码为0100b |

| #55到65 | 64.0GT/s | preset编码为0000b到1010b |

| #66到84 | 64.0GT/s | preset值为0000b |

- Setting Nos设置规则

- 在Fundamental Reset(warm reset/cold reset)后,第一次进入Polling.Compliance时设置序列号为#1

- 如果port支持16.0GT/s或者更高速度,在Polling.Configuration必须设置序列号为#1

- 后面每进一次polling.Compliance,次数加1,依次是#2,#3

- note : 在被动测试时为啥还会跟Polling.Configuration有关呢?因为被动测试时要让待测设备推测出Polling.Compliance时,仪器端必须得发送1ms 100MHz的信号。而根据协议规定,当发送pattern的速度为2.5GT/s时,并不需要进入EI在去把速度降到2.5GT/s,只有在Polling.Compliance状态的速度高于2.5GT/s才会先进入EI,把速度降到2.5GT/s,并且处于EI的时间必须大于1ms但是不高于2ms。所以当在Polling.Compliance时,本身速度就是2.5GT/s,不需要进入EI,当仪器发送1ms 100MHz的信号时,设备检测到任意一条lane退出EI,进入Polling.Active,这个时间很快,然后由于仪器还在发送信号,此时设备在Polling.Active状态就是认为有些lane退出过EI,不满足从没退出过EI,

4.1.2 Polling.Compliance确定compliance pattern类型

- 根据下列算法选择

| 原因 | compliance pattern类型 | |

|---|---|---|

| 收到8个连续的TS1OS进入Polling.Compliance(Compliance Receive bit为1,Loopback bit为0) | Modified Compliance Pattern | |

| Link Control 2寄存器中的Enter Compliance为1 | Link Control 2寄存器中的Enter Modified Compliance为1 | Modified Compliance Pattern |

| Link Control 2寄存器中的Enter Modified Compliance为0 | Compliance Pattern | |

| 没有检测到退出EI而进入Polling.Compliance | 根据进入Polling.Compliance的次数决定发送的compliance pattern类型 | |

- 没有检测到退出EI而进入Polling.Compliance

| 进入Polling.Compliance的次数 | 发送的compliance pattern类型 |

|---|---|

| #1到#25,#35到#45,#55到#65 | 所有lane上发送compliance pattern |

| #26,#46,#66 | 所有lane上发送Jitter Measurement Pattern |

| #27,#47,#67 | lane 0/8发送Jitter Measurement Pattern,其余所有lane发送Compliance Pattern |

| #28,#48,#68 | lane 1/9发送Jitter Measurement Pattern,其余所有lane发送Compliance Pattern |

| #29,#49,#69 | lane 2/10发送Jitter Measurement Pattern,其余所有lane发送Compliance Pattern |

| #30,#50,#70 | lane 3/11发送Jitter Measurement Pattern,其余所有lane发送Compliance Pattern |

| #31,#51,#71 | lane 4/12发送Jitter Measurement Pattern,其余所有lane发送Compliance Pattern |

| #32,#52,#72 | lane 5/13发送Jitter Measurement Pattern,其余所有lane发送Compliance Pattern |

| #33,#53,#73 | lane 6/14发送Jitter Measurement Pattern,其余所有lane发送Compliance Pattern |

| #34,#54,#74 | lane 7/15发送Jitter Measurement Pattern,其余所有lane发送Compliance Pattern |

| #75 | 所有lane发送High Swing Toggle Pattern |

| #76 | lane 0/8发送High Swing Toggle Pattern,其余所有lane发送Compliance Pattern |

| #77 | lane 1/9发送High Swing Toggle Pattern,其余所有lane发送Compliance Pattern |

| #78 | lane 2/10发送High Swing Toggle Pattern,其余所有lane发送Compliance Pattern |

| #79 | lane 3/11发送High Swing Toggle Pattern,其余所有lane发送Compliance Pattern |

| #80 | lane 4/12发送High Swing Toggle Pattern,其余所有lane发送Compliance Pattern |

| #81 | lane 5/13发送High Swing Toggle Pattern,其余所有lane发送Compliance Pattern |

| #82 | lane 6/14发送High Swing Toggle Pattern,其余所有lane发送Compliance Pattern |

| #83 | lane 7/15发送High Swing Toggle Pattern,其余所有lane发送Compliance Pattern |

| #84 | 所有lane上发送Low Swing Toggle Pattern |

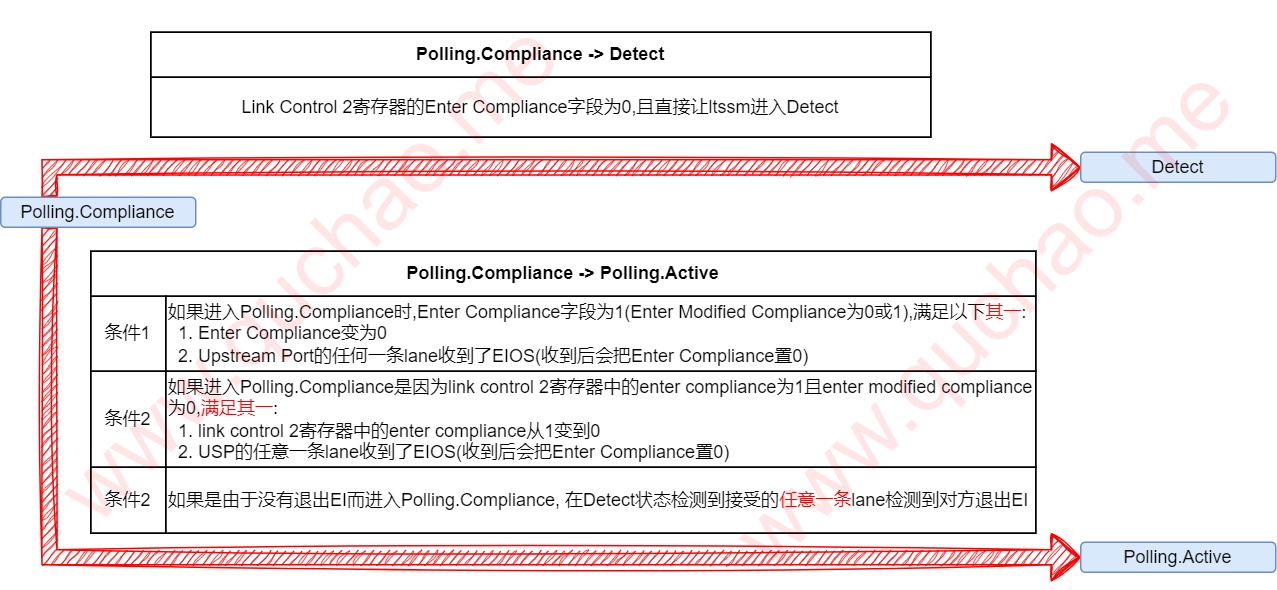

4.2 Polling.Compliance状态跳转

- Polling.Compliance可以实现的跳转

- Polling.Compliance -> Polling.Active

- Polling.Compliance -> Detect

4.2.1 Polling.Compliance -> Polling.Active

| 条件 | 跳转原因 |

|---|---|

| 条件1 | 如果进入Polling.Compliance时,Enter Compliance字段为1(Enter Modified Compliance为0或1),满足以下其一: 1. Enter Compliance变为0 2. Upstream Port的任何一条lane收到了EIOS(收到后会把Enter Compliance置0) |

| 条件2 | 如果进入Polling.Compliance是因为link control 2寄存器中的enter compliance为1且enter modified compliance为0,满足其一: 1. link control 2寄存器中的enter compliance从1变到0 2. USP的任意一条lane收到了EIOS(收到后会把Enter Compliance置0) |

| 条件3 | 如果是由于没有退出EI而进入Polling.Compliance, 在Detect状态检测到接受的任意一条lane检测到对方退出EI |

4.2.2 Polling.Compliance -> Detect

| 条件 | 跳转原因 |

|---|---|

| 条件1 | Link Control 2寄存器的Enter Compliance字段为0,且直接让ltssm进入Detect(如通过配置寄存器) |

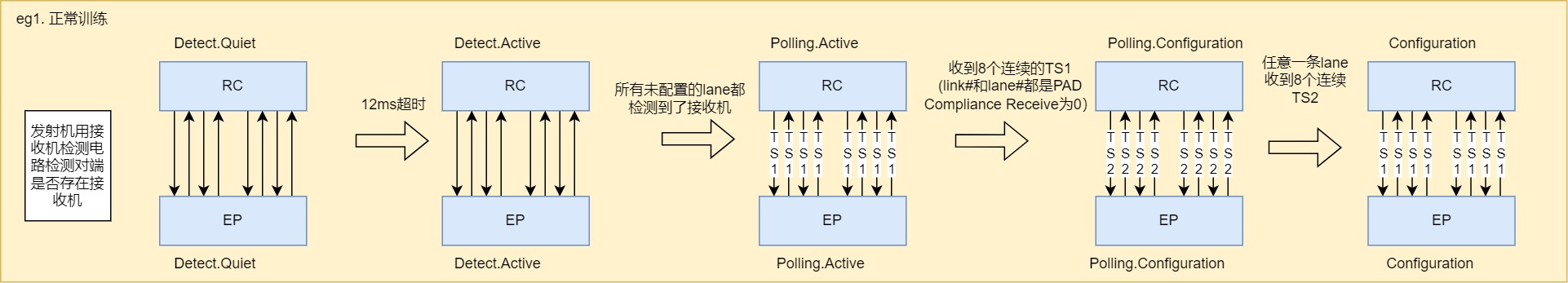

5. 例子

5.1 正常训练

进入polling.compliance的24ms超时,该时间从哪里算做起点?polling.active?

@Thomas 超时时间都是从进入某个状态开始算,比如“进入polling.compliance的24ms超时”,时间点从Polling.Active开始算,就是24ms超时后,满足跳转到Polling.Compliance的条件后就会往Polling.Compliance跳。设计中内部会有一个计数器,每进入一个状态都会清掉该计数器

@重新开始 谢谢解答

@重新开始 继续请问,“从Polling.Active开始算,就是24ms超时后”的超时是说无法正常进入polling.configuration引起的超时吗?

@Thomas 大概是你这个意思,就是说如果我自己所有的lane都能收到符合进入Polling.Configuration的TS1OS,那么很快就进入Polling.Configuration状态了(不会超时),但是如果有部分lane质量不好,它收不到符合TS1OS,那LTSSM就只能先等着,如果这部分lane(当然正常的lane很快就收到符合进入Polling.Configuration的TS1OS了)能在24ms内收到符合进入Polling.Configuration的TS1OS(也不会超时),如果信号质量不好的这部分lane一直都收不到TS1OS,那么就会24ms超时,但是也并不是说LTSSM就要进入Polling.Compliance, 因为你有部分lane是能收到TS1OS,也就是这部分lane是可以正常工作的,没有必要进入Polling.Compliance, Polling.Compliance状态主要用于测试用,没有异常,一般不会被动进入该状态。

进入Polling.Compliance的条件首先要24ms超时(怕后面看到的人引起误会,补充一下,此处说的超时不针对通过设置寄存器而进入Polling.Compliance的情况),其次,要不满足进入Polling.Configuration状态的条件。比如说:本端所有lane的TX和RX都连接到一个50欧姆的负载上,按照协议要求,它是可以进入Polling.Active状态的,但是由于对方是一个电阻,发不出来TS。因为本端所有的lane都收不到TS,且都没有退出EI,就会超时进入Polling.Compliance。

又或者说,

对方是一个真实的设备,但是由于工艺或者制造问题,发不出来连续的TS1OS或者发出来的TS1OS不对,这种情况本端也需要从Polling.Active进入Polling.Compliance(后续看到这个地方了,这样会直接进入detect,因为对方能发出TS就代表已经退出EI了,不满足往Polling.Compliance跳转的条件了)@重新开始 谢谢作者~强的一批 🐂🍺

@Alen 相互学习😁

@重新开始 谢谢作者,是要所有lane都接50欧姆电阻?还是TX的一条lane接50欧姆电阻能让所有lane进pollin.compliance呀

@Thomas pcie6.2的原话

协议原话是 “not all lanes” ,看对这个地方怎么理解了,不是所有lane都退出EI,

具体就得看设计者是怎么理解的,按照协议上来说,这两种理解都没啥问题。

@重新开始 感谢花费宝贵的时间解答,我实际尝试的是没有接电阻的lane,不会发compliance码型。

@Thomas 不客气,相互学习😁

@重新开始 作者您好,继续请教两个问题。

期待您的回复,谢谢!

@Thomas Hi,

可以直接退出,协议上规定了可以从Polling.Compliance直接退出到Detect,但是这部分怎么退协议没有规定,是基于具体实现的。

比如设计中可以设置一个寄存器xxx来控制是否LTSSM从Polling.Compliance直接进入Detect,当把这个寄存器配置为1,并且在Polling.Compliance阶段,Link Control 2寄存器的Enter Compliance位为0,在发完compliance pattern后就可以让LTSSM从Polling.Compliance退出到Detect,而不是退出到Polling.Active。

根据pcie spec 6.2。这个地方从Polling.Compliance退出到Polling.Active的条件还有一些哈,从Polling.Compliance退出到Polling.ative的条件还跟是怎么进入Polling.Compliance有关,比如是因为“没有检测到对方退出EI”而进入Polling.Compliance,从Polling.Compliance退出到Polling.Active还可以是在Detect状态检测到接受的任意一条lane退出EI(这个地方跟收到EIOS还是有点区别)。然后在回到你的问题上,收到EIOS后,Enter Compliance 比特还会从1置0吗?

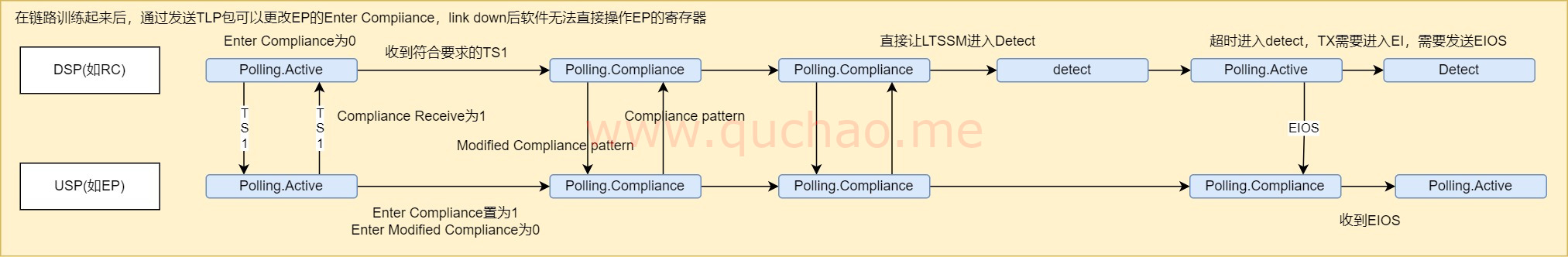

这得区分是DSP(Downstream Port如RC)还是USP(Upstream Port,如EP),对于USP来讲,收到EIOS后会把Enter Compliance置为0;对于DSP来说,并不会,但是或许DSP在退出Polling.Compliance后,Enter Compliance总是为0,除非在其它状态故意去设置这个寄存器。原因如下:

DSP进入Polling.Compliance的三种条件

USP进入Polling.Compliance的三种条件:

所以检测到至少1个EIOS,EP会把Enter Compliance置0,RC不会,但是RC在退出Polling.Compliance后,在不故意设置的情况下,Enter Compliance应该不会1。这些都是个人的理解,可能随着时间的推移,对这块会有新的理解。如果有哪里理解的不会,也欢迎共同探讨。

@重新开始 感谢感谢!还是您理解得透彻。

也就是说因为Enter compliance bit置1进入的,想要退出必须要置0。反之Enter compliance bit本身就为0,也就不需要置0。但是DSP为什么不会因为检测到EIOS而将Enter compliance bit置0没太看懂,您方便再讲讲吗?或者说DSP会因为检测到EIOS退出Polling.compliance吗?

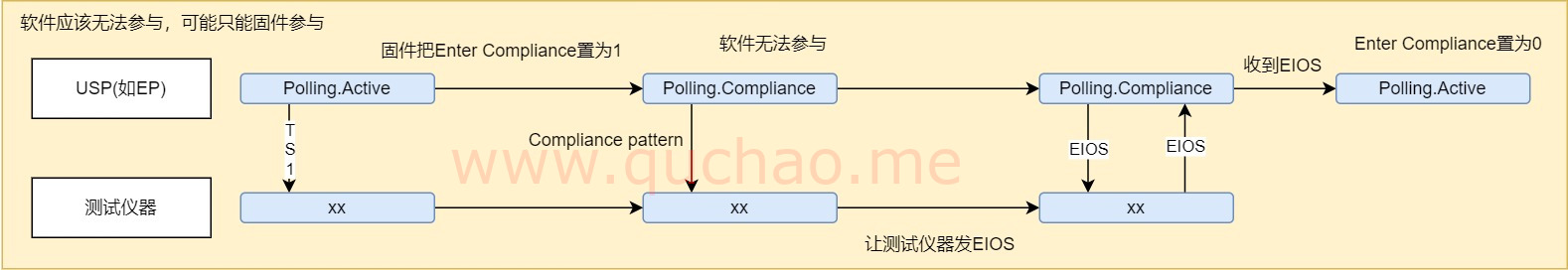

@Thomas 下面都是个人理解,如果进入Polling.Compliance是因为Enter Compliance比特,为什么USP在收到EIOS可以退出Polling.Compliance,而DSP在收到EIOS后不能退出Polling.Compliance。可能的原因是软件能否参与进来。

如果是DSP(如RC),软件是可以参与进来的,软件可以直接修改RC的寄存器。所以收到EIOS后不能退出Polling.Compliance,必须得配置Enter Compliance比特。

如果是USP(如EP),软件应该无法参与整个过程。

RC无论是连接的测试仪器还是实际设备,软件都可以直操作改寄存器。但是对于EP而言,软件不能参与整个过程。

eg1. EP直接连接的是测试仪器:

刚开始可以通过固件把link Control 2寄存器中给置1,当连接到测试仪器后,软件无法参与到这个过程中,这时就可以通过让测试仪器发EIOS,让EP退出Polling.Compliance并把Enter Compliance置0

eg2. 如果EP连接的是RC

链路训练起来后,可以通过TLP去配置EP的Enter Compliance,然后进行hot reset可以进入Polling.Compliance,在之后由于链路处于link down的一个状态,就无法通过发送TLP去更改EP中寄存器的值,就只能通过RC发送EIOS让EP退出Polling.Compliance状态

@重新开始 感谢感谢!太强了!

@Thomas 不客气,也是自己学习的一个过程,你不问的话,我可能都不会去想这些地方。

@重新开始 大师都谦虚。

还有个问题,就是我之前提到的,如果某条lane不接50欧姆电阻,就不会发出compliance pattern,那就是某条lane,进入了polling.compliance,而不是整个device。是这样理解吗?

@Thomas 不对,应该是Device进入polling.compliance,lane发不出pattern是因为终端开路,默认无设备连接。

@Thomas 对的,应该是你这样理解的。ltssm都是针对device,不针对lane,没接电阻,在detect状态认为该条lane没有接收机,这条lane就没发送数据的必要了

@重新开始 好的,谢谢~

@Thomas If the Port entered Polling.Compliance due to detecting eight consecutive TS1 Ordered Sets i… 阅读更多 »

@Thomas 个人理解如果需要能收到TS1OS,那对面可能不是一个测试仪器,因为TS1还是比较复杂,不确定测试仪器是否能够发出来。假如还是RC和EP连接。

对比compliance pattern和Modified Compliance Pattern,可以发现下面这些规律:

因此,Modified Compliance Pattern可能并不适合用来测试一些电气参数。

下面是我想到的一种场景,不确实是否符合真实情况。

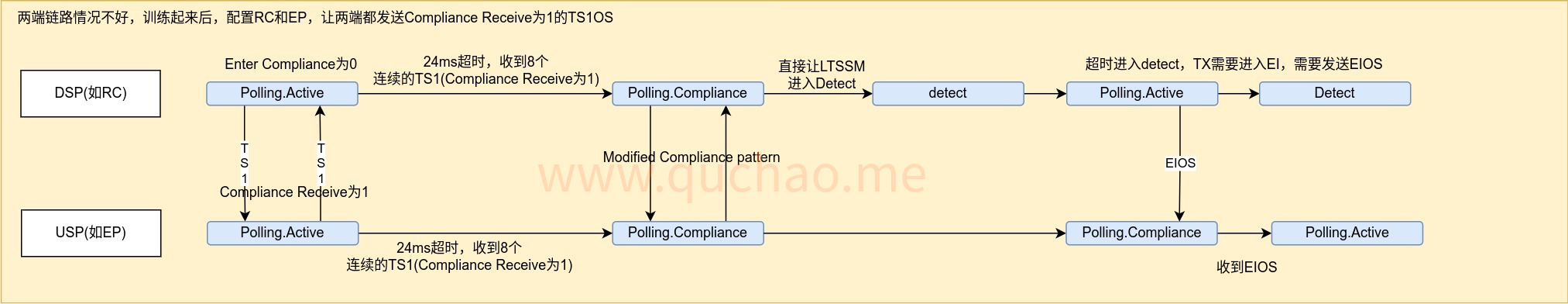

首先是两端都正常训练到L0,然后软件设置EP和RC的相关寄存器(非pcie spec标准寄存器,让两端发出去的TS1OS中的Compliance Receive为1。接着执行hot reset,让两端都进入Detect,然后进入Polling.Active。在该状态,两端都发送Compliance Receive为1的TS1OS,24ms超时后进入Polling.Compliance,然后开始发送Modified Compliance Pattern。发送Modified Compliance Pattern可能是为了判断链路的质量情况。

RC先进入Polling.Compliance发送Modified Compliance Pattern,其中Error Status为0,EP收到Modified Compliance Pattern后,会跟00h(gen3/4/5/6,因为Modified Compliance Pattern数据基本是00h构成,EIEOS和SKPOS很容易识别出来,gen1/2可能是跟compliance pattern比较)比较,如果收到的是一致的,就是在传输的过程中没有出错。如果EP收到的数据不是00h,那就是在传输过程了出现了错误,EP把Error Status加1,然后EP发送Modified Compliance Pattern中,Error Status为1。同样如果RC收到的数据跟00h对比,不一致就把Error Status加1,然后体现在发送出去的Modified Compliance Pattern中。当EP这边的Error Status计数到为127,EP如果再次收到的跟00h不一致的数据,Error Status仍然维持127(Error Status为8比特,计数到最大后不会清0)。Error Status反应的是本端TX和对端RX之间链路的质量情况,然后通过对端发送的Modified Compliance Pattern让本端知道该链路情况。当发完Modified Compliance Pattern后,如果收到的Modified Compliance Pattern中Error Status达到了127(这部分只是猜测),说明链路质量可能比较差,然后就可以换个速度,换个EQ参数继续测试,看看哪些情况下链路质量好,哪些情况下链路质量不好,然后对于链路质量不好的参数,就限制不使用这些参数。😂

— 2024-12-21 更新 start —

或者也可以测试RC内部的链路情况,比如说环回测试结合Modified Compliance Pattern,让RC的TX跟RX接在一起(或者配置寄存器让数据在内部环回),然后让本端的让RC发出去的Modified Compliance Pattern被自己的RX端接受到,大概能判断出内部的链路情况

— 2024-12-21 更新 end —

@重新开始 感谢作者这么晚还回复了很多。 但是SPEC的前半部分又提到,检测到8个连续的特定TS1OS会发送Compliance Pattern。所以是Modified Compliance Patt… 阅读更多 »

@Thomas 🐂,看的这么细,这个地方的Compliance Pattern应该就是泛指,跟协议中很多提到的TS1一样,有些都是泛指(根据具体情况,可能是EQ TS1或者是Modified TS1),下面这句话也是说的Compliance Pattern,就只提了Enter Compliance为1发Compliance Pattern,但是Enter Modified Compliance没提,那即可以为0也可以为1,如果为1要发Modified Compliance Pattern,跟这个地方也是有冲突的。所以应该都是泛指。

收到TS1OS就只发Modified Compliance Pattern,不会传输Compliance Pattern。原因可能就跟上面解释的一样,发Compliance Pattern好像没啥意义,如果RC跟EP接在一起,那也无法测试一些电气参数,发Modified Compliance Pattern还可以通过Error Status大概知道链路质量情况。所以就算RC跟EP连在一起,设置Enter Compliance为1,Enter Modified Compliance 为0让RC发Compliance Pattern,好像意义也不大。

@重新开始 谢谢!那比如说要做电气测试,就是除了TS1和Link Control 2 Register以外的方式(即超时)进入Polling.compliance,这时就会发用于测试的Compliance Pattern。可以这么理解吗?

@Thomas 不客气,我没做过测试哈,但是以我的理解,发送Compliance Pattern做电气参数测试,可以有2种方式:

所以除了超时之外,还可以设置寄存器让待测设备发送Compliance Pattern做电气参数测试。

协议也提到发送Modified Compliance Pattern可以测试BERT (Bit Error Rate Test,比特率误码测试)。

ps:测试仪器可能也可以发出TS1,比如误码仪实现了PCIE的物理层的状态机,但是上面提到的发送Modified Compliance Pattern作用以及分析应该还是成立的。误码仪也可以当成是一个设备。

ps:你以前问的一个问题

可能还要分一下情况

所以这个地方严格来讲还不能说是一条lane接50欧姆还是所有lane接50欧姆的事。

只是因为对测试来讲,不用的lane是开路,所以TX的一条lane接50欧姆电阻就能让LTSSM进入Polling.Compliance。哈哈,反正不确定的时候跟着协议走一遍,看满足哪个条件准没错,如果发现跟协议稍微有些不一致,那就以自己测试的为准,毕竟设计都不太可能跟协议完全一致。

@重新开始 感谢解惑,您是目前网上唯一把Polling.compliance说出来,说得清楚的,大部分都是一笔带过。回头看我提的几个问题,都比较简单,没仔细看SPEC,哈哈。总之感谢您抽出时间解答!

@重新开始 作者您好,我又来了 1.SPEC提到的Note是不是放在条件a下较为合适?即不是真实的设备,导致无法退出EI而进入Polling.Compliance。还是说编辑习惯放在一段的最后写Not… 阅读更多 »

@Thomas 是的,note可能放在条件a后面可能更合适。

条件b你可能是理解错了哈,它是针对在detect状态检测到接受机的这些lane,在detect状态正常是收不到TS的,detect状态主要是用来检测设备是否存在,而且如果就算是对端先发ts,本端在detect的行为其实并不关系是否收到了ts,本端只是认为对方退出了ei,然后本端也需要即时退出ei,进入到polling.active准备发ts。

条件b,它这句话的意思是:24ms之后,在detect状态检测到接受机的任意一条lane,如果在polling.active状态收到了8个连续的TS1OS,且ts中的enter compliance为1,本端就要进入polling.compliance。

detect状态是不能直接进入到polling.compliance。

因为polling.compliance不是正常链路训练的状态,正常链路训练肯定是不希望进polling.compliance,所以需要在polling.active一直等待可以进入configuration的ts,只有所有lane都收不到进入configuration的条件(规定的时间是24ms之内),才会考虑是进polling.compliance或者detect。这个地方肯定先考虑polling.compliance,因为detect状态就主要做一些接收机检测的工作,按理来说,最开始上电后就检测过接收机了,那我为啥还要在进detect状态呢,就是因为链路质量可能太差,导致链路训练有问题,连收到符合要求的ts都不能满足,只能进入detect再次检测一下是否所有的lane上是否都有接收机。

@重新开始 懂了,感谢解答~

重要的是Detect状态检测到的Lane,不是退出到Detect状态。

@重新开始 作者您好,再请教一个问题 b. Next state is Polling.Active if an exit of Electrical Idle is detected at the … 阅读更多 »

@Thomas

是的,针对的上一阶段是polling.compliance。

检测到EI不会从polling.compliance退出,只有检测到退出EI才从polling.compliance退出到polling.active。你说的检测到EI是指收到EIOS?

收到EIOS不是检测到EI,检测EI要么是pipe上的rx electric idle为高,要么是就是一段时间没收到东西(如L0期间长时间没收到SKPOS)。

也祝你周末越快。

@重新开始 好的谢谢,我理解错了,以为检测到EIOS和Electrical Idle是一个意思。前者是数据包,后者是状态。

结合之前我问的问题就是:

我的理解正确吗?

@Thomas 2,3理解应该没啥问题,但是有一点得注意,因为这些原因退出必须要是因为特定进入的原因才行,如果不是因为特定的原因进入,即使2和3满足也不一定会退出polling.compliance(比如因为设置寄存器进入,即使有lane检测到退出EI,也不能退出polling.comoliance)

1这里应该也没啥问题,需要注意是not all lane在里面设计中的具体实现。

@重新开始 谢谢大佬!全面又深入

没明白由于no lane exit EI而进入polling.compliance子状态的目的是?原先收不到TS1的lane在该状态岂不是继续收不到,难道说这种场景只是为了继续延长any lane EI exit的时间?但是又没说在该状态如果继续检测不到any lane EI exit该怎么办?

@aochen

没有lane退出EI而进入polling.compliance的目的是为了方便测试用。如果正常接的正常设备,双方交互TS,链路继续训练下去了。如果要测试信号质量,对面接的是测试仪器,只要保证测试仪器为等效50欧姆负载就可以让待测试设备进入polling.compliance,待测设备发动固定码型,便可测的一些电气参数。

进入polling.active状态时开始交互TS,如果对端没接设备而是测试仪器,收不到TS的lane也不应该收到TS,更准确的是RX electrical idle应该一直保持为高,即待测设备没进入polling.compliance时,测试仪器啥也不该发,不然待测设备无法进入polling.compliance。

继续检测不到任何lane退出EI,那就是24ms超时进入polling.compliance,因为已经满足进入polling.compliance的条件

举个例子:假如在detect检测到了4条lane

1.在polling.active只有2条lane退出,且24ms之内,这两条lane的任意一条能收到进入polling.configuration的TS,那么ltssm进入polling.configuration

2.在polling.active只有2条lane退出EI,但是在这两条lane上在24ms内收不到符合要求的TS,ltssm进入detect

3.24ms之内,在polling.active状态没有检测到任何lane退出EI,ltssm进入polling.compliance

明白了,进入compliance的前提是对端要接测试设备,谢谢博主细致的回答

@aochen 前面的回复可能有一点点误导性,这种方式是属于被动进入compliance,如果对面是真实的设备,通过配置标准寄存器也是可以进入compliance的哈。

明白,软件drive进入

在 Polling.Active -> Polling.Configuration 中有下面条件“任意一条lane收到8个连续的TS(或者TS的反),收到1个TS后最少需要发送1024个TS1,收到的TS需要满足下面其一”,请问作者,这句话怎么理解。

@tex 不清楚你是疑惑哪个点?

首先收到8个连续的TS是基本的要求,如果都收不到8个连续符合要求的TS,那可能就是链路不稳定或者太差,则在24ms内一直检查能否收到8个连续的TS,如果24ms都收不到,那也没有继续往下训练的必要了。至于为何会收到TS的反,因为本端差分线的rx-可能是连到对方的tx+,这样收到的TS1的标识符就不是4A,而是B5,所以极性的确定是在polling阶段。

收到1个TS1后需要发送1024个TS1可能是为了链路的稳定性(因为最开始识别到的TS是在cdr电路锁定后的,此时TS可能还不够稳定)。如果本端收到8个连续的TS1就跳走了而不发送1024个TS1的话,本端而后就开始发送TS2,对端收到TS2后也进入polling.configuration,开始发TS2,此时互发的TS2可能不够稳定,一端收到8个TS2,就只发送16个TS2,然后就到configuration状态发送TS1,在此状态总共发送TS2的数量较少,可能会导致另外一端无法收到8个连续的TS2,进而导致最后只有回到detect在重新训练,然后反复这样操作,可能会导致链路无法训练成功。

(直接在下面的楼层继续回复一直提示让我验证,重新开一楼)

感谢作者的讲解,明白您所描述的过程了。顺便提一下这个学习平台做的太好了!

想请问一下作者一个比较奇怪的问题。如果链路正常,进入polling.active状态后,再要进入polling.configuration状态是要检测到8个连续的TS1。要检测到TS1是需要实现块对齐吧?发送方需要在发TS1的同时,必须时不时地发送EIEOS来确保接收方能够获得块对齐?

这和我遇到的一个问题也有关。我在使用xilinx的pcie phy IP核的时候,x8链路每次测试时总是有部分lane达不到块对齐。我对pcie协议的实现做了简化,要求所有lane均能收到8个连续的TS1之后才能从polling.active跳转到polling.configuration,否则超时后跳回detect;我没有实现polling.compliance状态。但是实际上板测试的时候,ltssm总是不能正常跳转到polling.configuration.

看了您文章和评论区对polling.compliance状态的解释,您觉得这个问题和信号质量有关吗?

@wanderingxs

块对齐是 128b/130b 编码下存在的,协议中好像并没有说 8b/10b 编码也存在块的概念,128b/130b 编码中,2 比特 sync header 加上 128b 组成一个块。8b/10b 下不同 lane 上 COM 字符可能存在 skew,可能你是想说这个?但是在

Polling状态也不需要 de-skew, de-skew 可以参考另外一篇博文针对初次训练,在

Polling状态时是不会发 EIEOS, EIEOS 发送规则可以看另外一篇博文EIEOS 部分,EIEOS 是 gen2 引入的,所以在 < code>Polling 状态时是不会发送 EIEOS 的。按照协议规定,在

Polling状态,首先需要至少发送 1024 个 TS1OS,来保证对端 CDR 能够从比特流中恢复出时钟和数据,如果 CRD 不能锁定数据,那么 PHY 就不会将正确的数据送到 MAC,就可能造成某些 lane 无法收到 8 个连续的 TS1OS。我认为大概率可能跟信号质量有关。从

Polling.Active状态按照协议也可以 24ms 超时后,任意一条收到符合要求的 TS1OS 后进入Polling.Configuration,但是在Polling.Configuration需要所有 的 lane 都收到符合要求的 TS2OS,可能就有考虑到在。但是从你的实现上来看,24ms 超时后就进入了Polling.Active状态,可能不是所有的 lane 信号质量都很好,24ms 超时进入Polling.Configuration之后,还允许部分信号质量不好的 lane 在继续尝试Detect状态,你可以将这里的情况完善一下,按照协议的要求来做,看会不会有改善。当然如果有条件,可以进行 compliance 测试来直接验证信号质量。回答有些仓促,如哪些地方有错或者不严谨,欢迎共同探讨,一起学习。

@重新开始 谢谢博主的回复!ヾ(≧∇≦*)ゝ

我之前的回复遗漏了一个要点:pcie1.0或2.0速率下链路是可以正常建立的;但是pcie3.0或4.0下由于部分lane总是不能收到连续的8个TS1(更确切地说,部分lane什么数据都收不到),导致我之前实现的简化版ltssm一直卡在polling.active状态。我打算按照您的建议,根据协议完善下ltssm,看看会不会有改善。

这里捉个虫,按照协议polling.configuration -> Configuration的状态跳转,也只需要detect状态下有检测到接收方的任意一个lane,检测到8个连续的TS2即可。

此外我注意到,xilinx PCIe PHY IP核中,对于使用128b/130b编码的数据流,RX端的数据通路是:SIPO -> 128b/130b decoder -> Block Detect Align -> PCIe RX buffer -> RX Interface -> PCIe MAC。在polling.active状态下,对端TX必须发送1024个以上的TS1OS,本端RX CDR才有可能正常恢复出时钟和数据,然后经过上述数据通路,将收到的TS1OS送到MAC,是这样吗?

@重新开始 谢谢博主的回复!ヾ(≧∇≦*)ゝ

我之前的回复遗漏了一个要点:pcie1.0或2.0速率下链路是可以正常建立的;但是pcie3.0或4.0下由于部分lane总是不能收到连续的8个TS1(更确切地说,部分lane什么数据都收不到),导致我之前实现的简化版ltssm一直卡在polling.active状态。我打算按照您的建议,根据协议完善下ltssm,看看会不会有改善。

但是在 Polling.Configuration 需要所有的 lane 都收到符合要求的 TS2OS

这里捉个虫,按照协议polling.configuration -> Configuration的状态跳转,也只需要detect状态下有检测到接收方的任意一个lane,检测到8个连续的TS2即可。

此外我注意到,xilinx PCIe PHY IP核中,对于使用128b/130b编码的数据流,RX端的数据通路是:SIPO -> 128b/130b decoder -> Block Detect Align -> PCIe RX buffer -> RX Interface -> PCIe MAC。在polling.active状态下,对端TX必须发送1024个以上的TS1OS,本端RX CDR才有可能正常恢复出时钟和数据,然后经过上述数据通路,将收到的TS1OS送到MAC,是这样吗?

@wanderingxs 😂确实,记错了,所有lane是

Configuraion.Idle到L0的要求,从Polling.Configuration到Configuration跳转条件我上面图上都还是写的任意一条lane😅。 gen1/2/正常的话,可能要考虑一下gen3/4下一些EQ参数是否是最优的,EQ参数没设置好的话,可能会导致后续在Recovery.RcvrLock无法锁住数据,只能先降速。降完速还是有问题的话, 就会降宽度,如果降完宽度还是不行,就只有重新进入Detect状态。因为一进入

Detect状态后,链路速度就会降到2.5GT/s,而Polling状态只能从Detect进入,即只要在Polling状态时,链路的速度就是2.5GT/s,2.5GT/s你可以关注一下数据流,通路应该不会经过128b/130b decoder,从pipe上而言,是经过的8b/10b decoder。如果能看到两端的状态机变化,可能会更加容易分析问题所在。

@重新开始 明白了,谢谢您的耐心解答😊