CDC—-亚稳态

时钟域

同步电路(同步时钟域):由同步时钟驱动的电路。

异步电路(异步时钟域):电路中存在异步时钟的部分。

同步时钟:必然同源,其频率或相位有固定关系的时钟。比如时钟及其2/4/..分频时钟。

异步时钟:(不同源)

(1)两时钟频率不同,因而相位关系也是变化的,因此异步。

(2)两时钟频率相同,但由于不同源相位关系变化。—-(是因为不同源导致频率无法精确相同,其jitter变化不同,导致两时钟相位不同)

Q: 同源 有可能生成两个异步时钟吗? A:应该不能..

D触发器的亚稳态

触发器原理

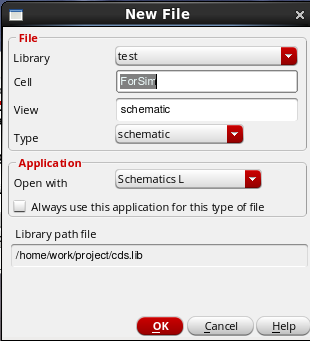

集成电路中常使用触发器对信号寄存,以D触发器为例,如下图所示。

…….D触发器图。

亚稳态的出现:

触发器要求D必须在建立/保持时间内保持稳定,且复位的释放要在移除/恢复时间之外。否则触发器输出将呈现亚稳态现象,即输出非"0"非"1"的信号值。

(1)输入D的建立/保持时间

当输入信号D 在时钟上升沿(默认上升沿为采样边沿)之前的建立时间内,或之后的保持时间内变化时,将导致输出Q产生亚稳态。

(2)复位rst的移除/恢复时间

当复位信号rst 在时钟上升沿(默认上升沿为采样边沿)之前的移除时间内,或之后的恢复时间内释放时,将导致输出Q产生亚稳态。

亚稳态的特点和危害

两个特点:(1)亚稳态的持续时间是不确定的。(2)亚稳态最终稳定到的状态是不确定的。 亚稳态的持续时间与工艺相关,也与实际芯片电路运行场景相关,受到轻微扰动后可能恢复稳定,扰动可能使其稳定到低或高电平。

亚稳态的危害:亚稳态可能传播到后续电路,导致电路震荡,产生毛刺,逻辑错误等灾难。…..

如何降低亚稳态概率

实际电路中,由于异步时钟域的存在,对于接受时钟域来说,其触发器的输入信号变化时间是不确定的,亚稳态是难以避免的。那么,应该如何降低亚稳态概率呢?

这里提出MTBF(Mean Time Between Failure,平均无故障时间),可看做一个触发器的MTBF。而亚稳态发生概率可认为是1/MTBF。

$MTBF=\frac{e(t_{\tau}/{\tau})}{Wf_ef_d}$

其中,参数..

对于系统级的亚稳态发生概率,可以理解为所有sync chain 的亚稳态发生概率之和。 因此由于短板效应,1/MTBF较大的sync chain将显著影响系统故障率。为了降低单条sync chain 亚稳态发生概率即提高MTBF,可从以下几个方面入手。

(1)减小Tw和Tc:使用更先进的器件。

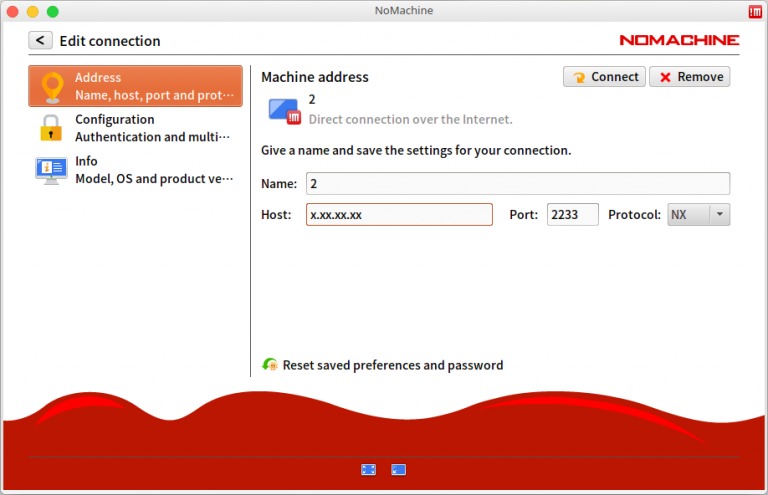

(2)增加Tmet:

- 增加sync chain 级数(即FF个数)

- 优化的sync cell (减小Tsu,Tco)

- Sync chain间线延时减少,时钟偏斜减少(减小Tskew和Tpath)

- 避免sync chain间的scan等逻辑(减少Tpath)

Q: 亚稳态可以完全消除吗? A: 不能,只能降低亚稳态概率。 由于MTBF只能设置成很大很大,而1/MTBF实际上永远是个大于0的数,即亚稳态发生概率必然不能为0,因此亚稳态不能被消除,只能通过降低其概率来避免实际电路运行时的亚稳态灾难。

🐂🍺

求更新